# X-RAY RADIATION DAMAGE STUDIES AND DESIGN OF A SILICON PIXEL SENSOR FOR SCIENCE AT THE XFEL

# Dissertation

zur Erlangung des Doktorgrades des Fachbereichs Physik der Universität Hamburg

vorgelegt von **Jiaguo Zhang**aus Liaoning of China

(中国·辽宁)

Hamburg 2013

Gutachter der Dissertation: Prof. Dr. Robert Klanner

Prof. Dr. Wolfgang Hansen

Gutachter der Disputation: Prof. Dr. Peter Schleper

Prof. Dr. Erika Garutti

Datum der Disputation: 30.05.2013

Vorsitzender des Prüfungsausschusses: Dr. Georg Steinbrück

Vorsitzender des Promotionsausschusses: Prof. Dr. Peter Hauschildt

**Dekan der MIN Fakultät:** Prof. Dr. Heinrich Graener

Leiter des Department Physik: Prof. Dr. Daniela Pfannkuche

#### **Abstract**

Experiments at the European X-ray Free Electron Laser (XFEL) require silicon pixel sensors which can withstand X-ray doses up to 1 GGy. For the investigation of X-ray radiation damage up to these high doses, MOS capacitors and gate-controlled diodes built on high resistivity n-doped silicon with crystal orientations <100> and <111> produced by four vendors, CiS, Hamamatsu, Canberra and Sintef, have been irradiated with 12 keV X-rays at the DESY DORIS III synchrotron-light source. Using capacitance/conductance-voltage, current-voltage and thermal dielectric relaxation current measurements, the densities of oxide charges and interface traps at the Si-SiO<sub>2</sub> interface, and the surface-current densities have been determined as function of dose. Results indicate that the dose dependence of the oxide-charge density, the interface-trap density and the surface-current density depend on the crystal orientation and producer.

In addition, the influence of the voltage applied to the gates of the MOS capacitor and the gate-controlled diode during X-ray irradiation on the oxide-charge density, the interface-trap density and the surface-current density has been investigated at doses of 100 kGy and 100 MGy. It is found that both strongly depend on the gate voltage if the electric field in the oxide points from the surface of the SiO<sub>2</sub> to the Si-SiO<sub>2</sub> interface.

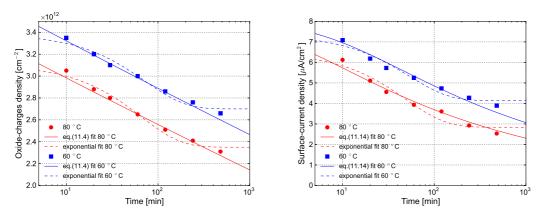

To verify the long-term stability of irradiated silicon sensors, annealing studies have been performed at 60  $^{\circ}$ C and 80  $^{\circ}$ C on MOS capacitors and gate-controlled diodes irradiated to 5 MGy as well, and the annealing kinetics of oxide charges and surface current were determined.

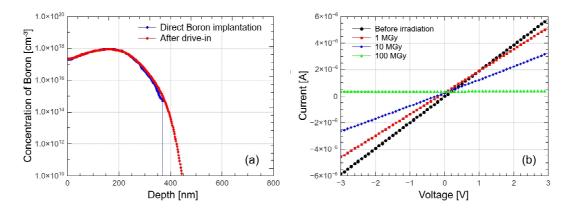

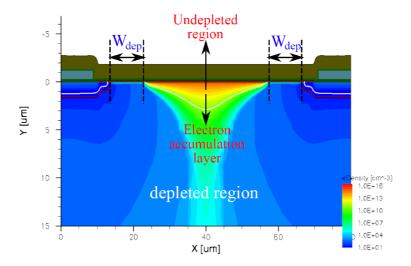

Moreover, the macroscopic electrical properties of segmented sensors have slao been investigated as function of dose. It is found that the defects introduced by X-rays increase the full depletion voltage, the surface leakage current and the inter-electrode capacitance of the segmented sensor. An electron-accumulation layer at the  $\text{Si-SiO}_2$  interface is observed. Its width increases with dose and decreases with applied bias voltage. The electron-accumulation layer is relevant for the change of the electrical properties of segmented sensors.

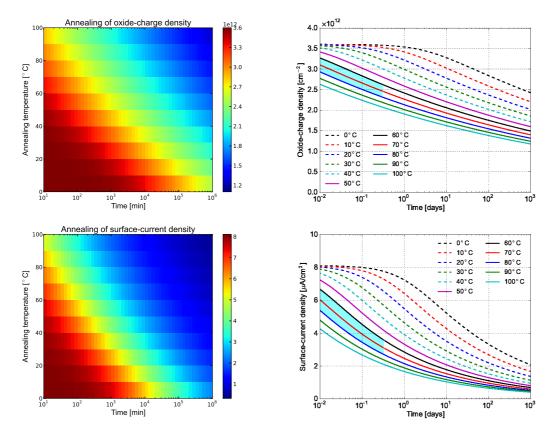

Finally, according to the optimum parameters of silicon pixel sensors from TCAD simulations taking the damage-related parameters into account, a radiation-hard silicon pixel sensor for the AGIPD Project has been designed.

#### Kurzfassung

Die an dem *European X-ray Free Electron Laser* (XFEL) geplanten Experimente werden Silizium-Pixel-Sensoren erfordern, die Röntgen-Dosen bis zu 1 GGy standhalten können. Für die Untersuchung der Strahlenschäden bei solch hohen Dosen wurden MOS-Kondensatoren sowie Gate-gesteuerte Dioden mit 12 keV Röntgenstrahlen der DESY DORIS-III Synchrotronquelle bestrahlt. Die verwendeten Strukturen wurden auf n-dotiertem Silizium mit hohem Widerstandswert und mit den Kristallorientierungen <100> sowie <111> von vier verschiedenen Herstellern gefertigt (CiS, Hamamatsu, Canberra und Sintef). Mit Hilfe von Messungen der Kapazität, der Konduktivität und des Stroms als Funktion der angelegten Spannung, sowie TDRC-Messungen (*Thermal Dielectric Relaxation Current*), wurden die Dichten von Oxydladungen und Interface-Traps an dem Si-SiO<sub>2</sub> Übergang, sowie die Oberflächen Stromdichten als Funktion der Strahlendosis bestimmt. Die Ergebnisse zeigen, dass die Dosisabhängigkeit der Oberflächendichte, der Oxydladungen und der Oberflächen Stromdichte von der Kristallorientierung und dem Hersteller abhängen.

Darüber hinaus wurde der Einfluss der während der Röntgenbestrahlung an den Gates des MOS-Kondensators und an der Gate-gesteuerten Diode anliegenden Spannung auf die Oxid-Ladungsdichte, auf die Dichte der Traps an der Grenzfläche sowie auf die Oberflächen-Stromdichte im Dosisbereich von  $100\,\mathrm{kGy}$  bis  $100\,\mathrm{MGy}$  untersucht. Dabei wurde herausgefunden, dass diese stark von der angelegten Spannung abhängen, falls das elektrische Feld in dem Oxid von der Oberfläche des SiO<sub>2</sub> zu der Si-SiO<sub>2</sub> Grenzfläche zeigt.

Um die langfristige Stabilität der bestrahlten Silizium-Sensoren zu überprüfen, wurden *annealing-*Studien bei 60°C und 80°C mit bis zu 5 MGy bestrahlten MOS-Kondensatoren und Gate-gesteuerten Dioden durchgeführt und so das Ausheilverhalten der Oxidladungen und des Oberflächenstroms bestimmt.

Weiter wurden die makroskopischen elektrischen Eigenschaften von segmentierten Sensoren als Funktion der Dosis untersucht. Es wurde dabei festgestellt, dass die durch Röntgenstrahlung verursachten Schäden die Verarmungsspannung, den Oberflächen Leckstrom und die Kapazität zwischen den Elektroden des segmentierten Sensors erhöhen. Eine Elektron-Akkumulationsschicht an der Si-SiO<sub>2</sub> Schnittstelle wurde beobachtet. Dessen Breite wächst mit der Dosis und nimmt mit der angelegten Spannung ab. Die Elektron-Akkumulationsschicht ist von Bedeutung für die Veränderung der elektrischen Eigenschaften von segmentierten Sensoren.

Die somit gewonnenen Erkenntnisse zu Strahlenschäden in Silizium-Pixel-Sensoren erlaubten das Optimieren der relevanten Paramter mit Hilfe von TCAD-Simulationen und letztendlich die Entwicklung eines strahlenharten Pixel-Sensors für das AGIPD-Projekt.

#### 摘要

在欧洲X射线自由电子激光上所要进行的实验中,硅像素传感器将被广泛使用。在三年的使用期中,传感器所接受的X射线辐射剂量为1 GGy。为了评估X射线对传感器所引起的辐射损伤,对基于高阻硅材料的MOS管和门控二极管进行了辐照。所选用的MOS管和门控二极管由CiS、Hamamatsu、Canberra和Sintef半导体公司生产。在DORIS III同步辐射光源上完成了对这些测试结构的辐照工作,辐照选用了12 keV的X射线。辐照后,对MOS管和门控二极管的电学性质进行了测量,其中包括电容/电导-电压曲线,电流-电压曲线,以及热介电松弛电流随温度的变化曲线。通过上述测量,获得了氧化层电荷的密度、硅-二氧化硅界面陷阱的密度,以及表面电流密度随剂量变化的关系。实验结果表明氧化层电荷、界面陷阱以及表面电流的密度在高剂量辐照后对硅的晶向和半导体生产过程中所使用的技术存在依赖关系。

此外,实验上观测了在辐照过程中应用于MOS管和门控二极管的门电压对于氧化层电荷、界面陷阱以及表面电流所造成的影响。研究发现:如果二氧化硅层内的电场由二氧化硅表面指向硅-二氧化硅界面,由辐射所引发的上述物理量对门电压具有较强的依赖性。

为了验证经过辐照的硅传感器的电学性质具有长期稳定性,对辐照5 MGy剂量的MOS管和门控二极管进行了高温退火研究。退火温度选取60摄氏度和80摄氏度。此工作确定了氧化层电荷和表面电流的退火动力学:二者在不同温度下随时间的变化可以用幂函数表述。基于该工作,幂函数中的未知参数得以确定,以此可预测其余温度下氧化层电荷和表面电流的退火行为。

另外,对硅条形传感器辐射后的宏观电学性质进行了观测。实验发现: X射线所引起的辐射损伤可以增加全耗尽电压、增大暗电流以及电极之间的电容值。测量结果表明在硅晶体内部、硅-二氧化硅界面下形成了一个电子累积层。电子累积层的宽度随辐射剂量值的增大而增大、随传感器偏压值的增大而减小。此电子累积层与条形探测器电学性质的变化息息相关。

最后,使用有限元数值模拟程序对硅像素传感器的几何参数进行了优化。在模拟中考虑并输入了与辐射损伤相关的参数,这些参数由上述实验获得。根据优化结果,为AGIPD探测器设计了抗辐射的硅像素传感器。

# Contents

| 1. | Intro | oduction                                                                           | 1  |

|----|-------|------------------------------------------------------------------------------------|----|

|    | 1.1.  | The detector projects for the XFEL: AGIPD, LPD and DSSC                            | 2  |

|    | 1.2.  | Motivation and structure of this thesis                                            | 2  |

| 2. | Prop  | perties of silicon crystals                                                        | 5  |

|    | 2.1.  | Crystal structure of Si                                                            | 5  |

|    | 2.2.  | Band structure of silicon                                                          | 6  |

|    | 2.3.  | Intrinsic and non-intrinsic silicon                                                | 6  |

|    | 2.4.  | Transport of carriers                                                              | ç  |

|    | 2.5.  | Generation and recombination of carriers                                           | 11 |

| 3. | Rad   | iation damage induced by X-rays                                                    | 13 |

|    | 3.1.  | Bulk and surface damage                                                            | 13 |

|    | 3.2.  | Basic mechanisms of surface damage                                                 | 18 |

|    | 3.3.  | Modelling of damage mechanisms                                                     | 20 |

|    | 3.4.  | Factors influencing the densities of oxide charges and interface traps             | 24 |

|    | 3.5.  | <b>1 1</b>                                                                         | 27 |

|    | 3.6.  | Characteristic parameters of surface damage                                        | 28 |

|    |       | 3.6.1. Oxide-charge density $N_{0x}$                                               | 28 |

|    |       | 3.6.2. Interface-states density $D_{it}(E_{it})$ and the integrated value $N_{it}$ | 29 |

|    |       | 3.6.3. Surface-current density $J_{surf}$                                          | 29 |

| 4. | Silic | on test structures for damage characterization                                     | 31 |

|    | 4.1.  | Pad diode                                                                          | 31 |

|    | 4.2.  | MOS capacitor                                                                      | 34 |

|    | 4.3.  | Gate-controlled diode (GCD)                                                        | 38 |

|    | 4.4.  | MOS Field Effect Transistor (MOSFET)                                               | 39 |

| 5. |       | surement set-ups and principles                                                    | 43 |

|    | 5.1.  | C/G-V and I-V measurements                                                         | 43 |

|    | 5.2.  | TDRC measurements                                                                  | 44 |

|    |       | 5.2.1. TDRC principles                                                             | 45 |

|    |       | 5.2.2. TDRC set-up and measurement procedure                                       | 47 |

| 6. |       | del calculation for MOS capacitors                                                 | 49 |

|    | 6.1.  | 1                                                                                  | 49 |

|    |       | 6.1.1. The capacitance and conductance of the insulator                            | 49 |

|    |       | 6.1.2. The capacitance of the depletion layer and inversion capacitance            | 50 |

|    |       | 6.1.3. The recombination/generation resistance                                     | 52 |

### Contents

|    |       | 6.1.4. The capacitance and conductance due to interface traps              | 55   |

|----|-------|----------------------------------------------------------------------------|------|

|    |       | 6.1.5. The capacitance and conductance of the non-depleted silicon         | 55   |

|    |       | 6.1.6. The admittance of the entire circuit                                | 55   |

|    |       | 6.1.7. Relation between gate voltage and band bending                      | 56   |

|    | 6.2.  | Comparisons between the model calculation and TCAD simulation              | 56   |

|    |       | 6.2.1. C/G-V curves of MOS capacitors without/with oxide charges .         | 57   |

|    |       | 6.2.2. C/G-V curves of MOS capacitors with a single interface-trap level   | l 57 |

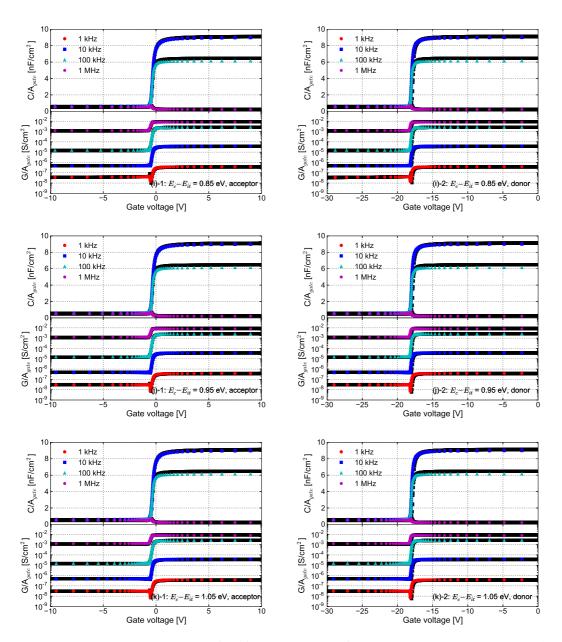

|    |       | 6.2.3. C/G-V curves of MOS capacitors with distributed interface trap      | 59   |

|    | 6.3.  | Investigation of "invisible" electrical properties of MOS capacitors       | 59   |

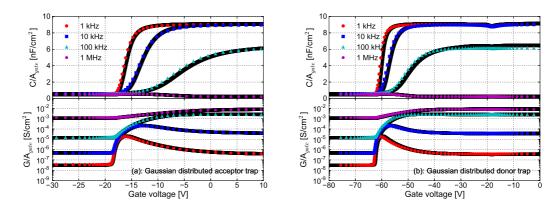

|    |       | 6.3.1. The charge stored in the interface trap                             | 59   |

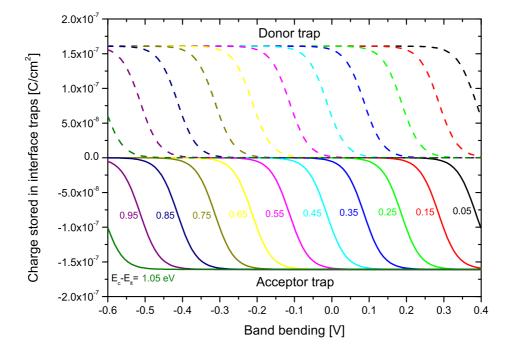

|    |       | 6.3.2. The interface-trap capacitance, conductance and time constant .     | 59   |

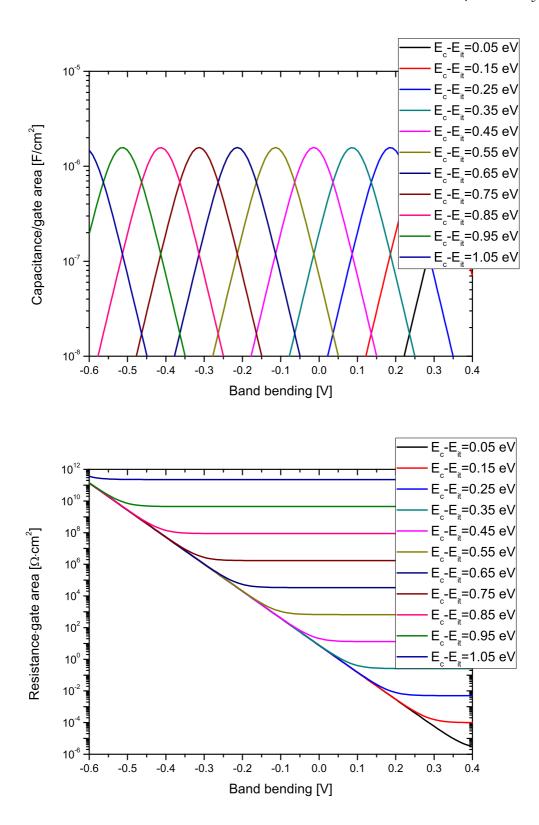

|    | 6.4.  | Summary                                                                    | 60   |

| 7. | Irrac | liation procedure                                                          | 67   |

|    | 7.1.  | Irradiation facility                                                       | 67   |

|    | 7.2.  | Beam profile                                                               | 67   |

|    | 7.3.  | Calibration of the dose                                                    | 71   |

| 8. | Met   | hods to extract $N_{ox}$ , $N_{it}$ and $J_{surf}$                         | 75   |

|    | 8.1.  | Extraction of $N_{it}$ and $N_{ox}$                                        | 75   |

|    |       | Extraction of $J_{surf}$                                                   | 80   |

|    | 8.3.  | Summary and discussion                                                     | 84   |

| 9. |       | e dependence of $N_{ox}$ , $N_{it}$ and $J_{surf}$                         | 85   |

|    | 9.1.  | Investigated structures and their electrical properties before irradiation | 85   |

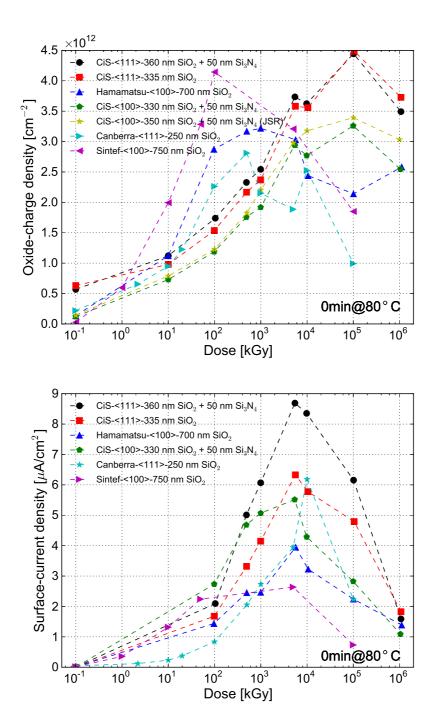

|    | 9.2.  | Measurements after irradiation                                             | 87   |

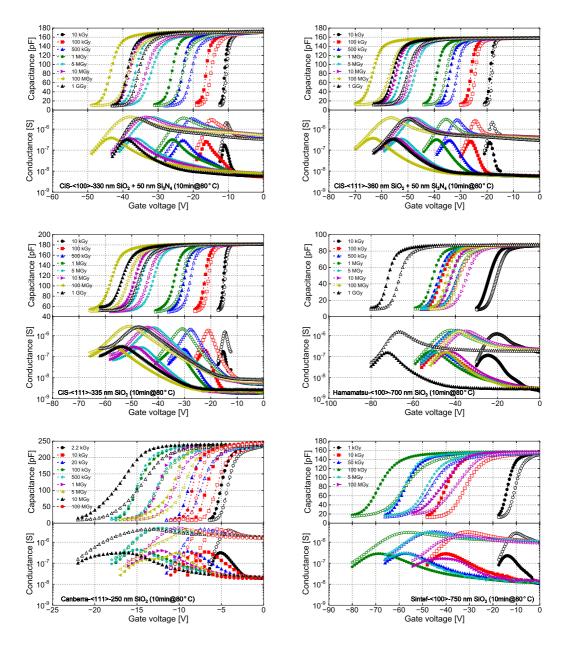

|    |       | 9.2.1. C/G-V curves of MOS capacitors                                      | 88   |

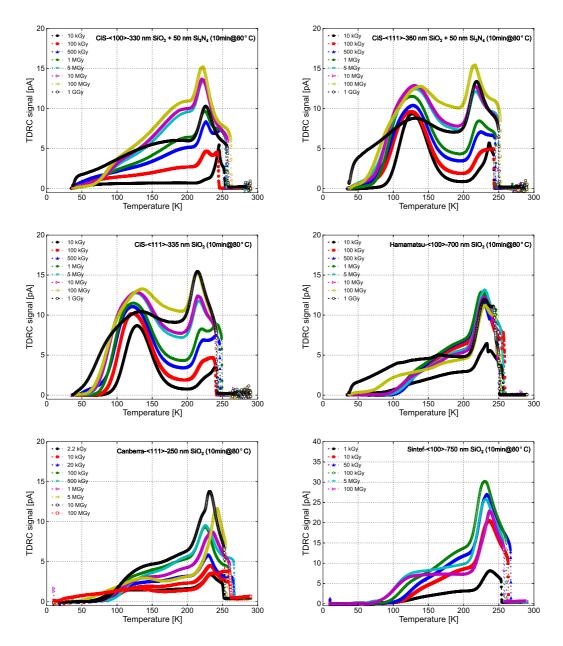

|    |       | 9.2.2. TDRC spectra of MOS capacitors                                      | 90   |

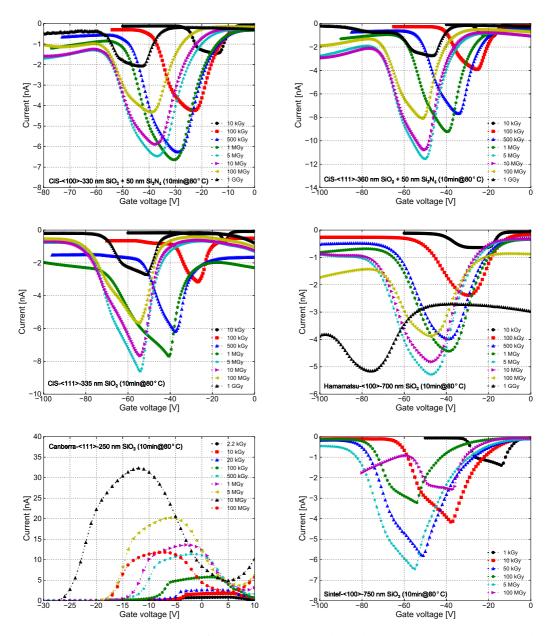

|    |       | 9.2.3. I-V curves of gate-controlled diodes                                | 91   |

|    | 9.3.  |                                                                            | 92   |

|    | 9.4.  | Summary                                                                    | 98   |

| 10 |       | e-voltage dependence of $N_{ox}$ , $N_{it}$ and $J_{surf}$                 | 99   |

|    |       | Investigated structures and their electrical properties before irradiation | 99   |

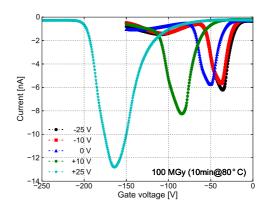

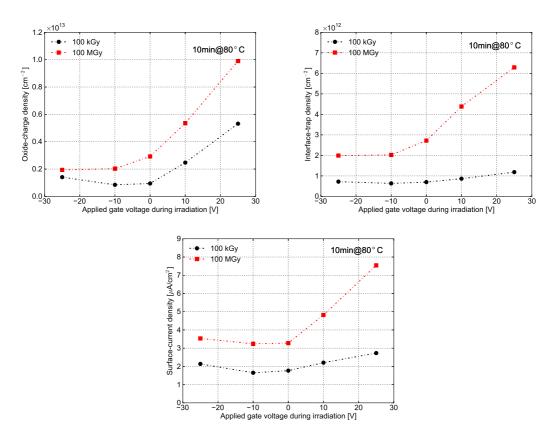

|    | 10.2. |                                                                            | 100  |

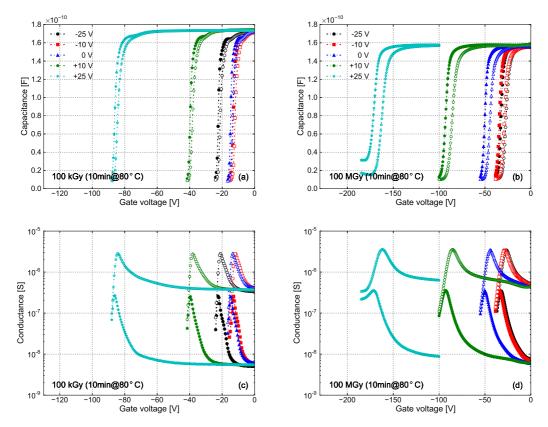

|    |       | 10.2.1. C/G-V curves of MOS capacitors                                     |      |

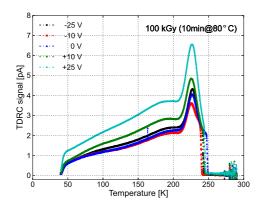

|    |       | 10.2.2. TDRC spectra of MOS capacitors                                     |      |

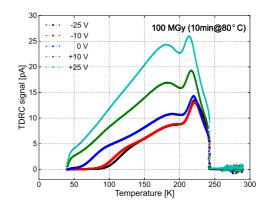

|    |       | 10.2.3. I-V curves of gate-controlled diodes                               |      |

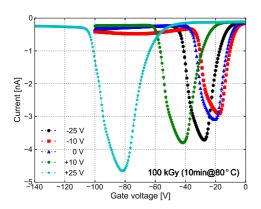

|    |       | Results: $N_{ox}$ , $N_{it}$ and $J_{surf}$ vs. $V_{irrad}$                |      |

|    | 10.4. | Summary                                                                    | 105  |

| 11 |       | 0.000 11 75011 7                                                           | 107  |

|    | 11.1. | e                                                                          | 107  |

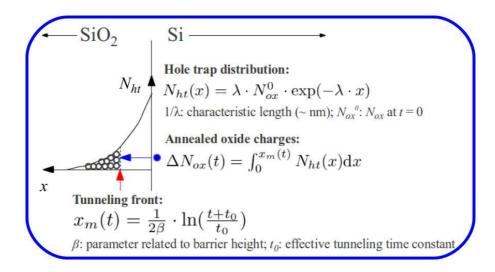

|    |       | 11.1.1. Annealing model for oxide charges                                  |      |

|    |       | 11.1.2. Annealing model for interface traps                                |      |

|    | 11.2. | Investigated structures and their electrical properties before irradiation | 110  |

|    | 11.3. Measurements after irradiation                                               | . 111 |

|----|------------------------------------------------------------------------------------|-------|

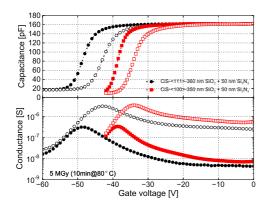

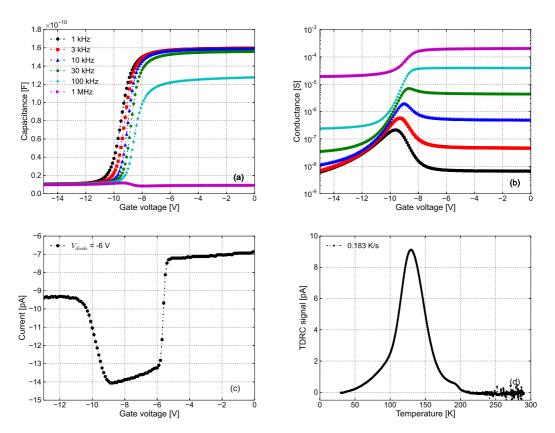

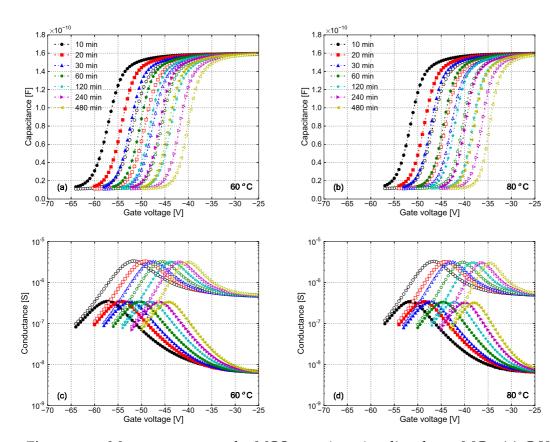

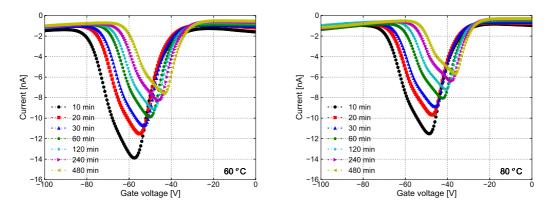

|    | 11.3.1. C/G-V curves of MOS capacitors                                             |       |

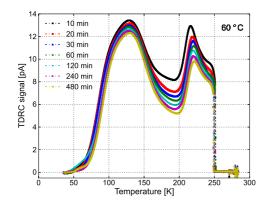

|    | 11.3.2. TDRC spectra of MOS capacitors                                             |       |

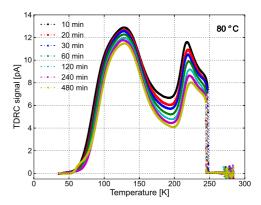

|    | 11.3.3. I-V curves of gate-controlled diodes                                       | . 114 |

|    | 11.4. Results: $N_{ox}$ and $J_{surf}$ vs. annealing                               | . 115 |

|    | 11.5. Summary                                                                      |       |

|    |                                                                                    | . 11/ |

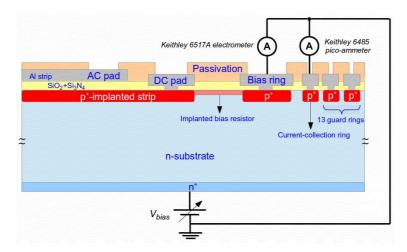

| 12 | . Characterization of electrical properties of p <sup>+</sup> n microstrip sensors | 119   |

|    | 12.1. Investigated sensors                                                         | . 119 |

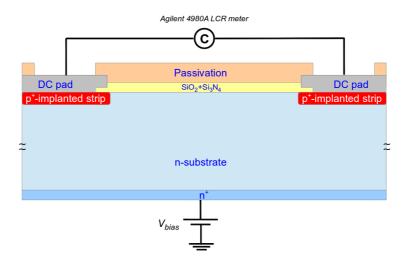

|    | 12.2. Change of electrical properties of microstrip sensors with irradiation .     | . 120 |

|    | 12.2.1. Bias resistance                                                            | . 121 |

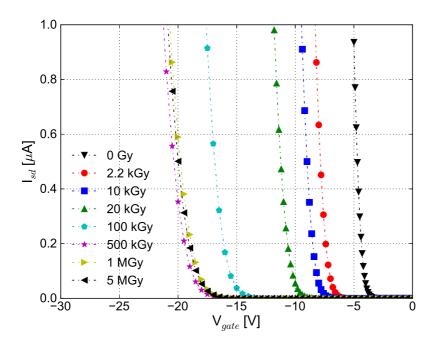

|    | 12.2.2. Full depletion voltage                                                     | . 122 |

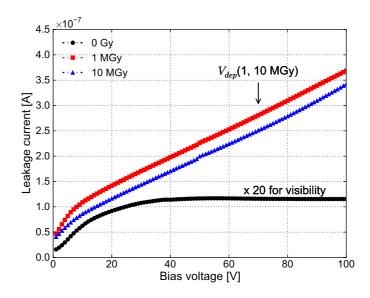

|    | 12.2.3. Leakage current                                                            | . 125 |

|    | 12.2.4. Interstrip capacitance                                                     |       |

|    | 12.2.5. Interstrip resistance                                                      |       |

|    | 12.2.6. Coupling capacitance                                                       |       |

|    | 12.3. Change of electrical properties of microstrip sensors irradiated with bi     |       |

|    | 12.3.1. Sensor capacitance                                                         |       |

|    | 12.3.2. Leakage current                                                            |       |

|    | 12.3.3. Interstrip capacitance                                                     |       |

|    | 12.4. Summary and relevance to AGIPD sensor                                        |       |

|    |                                                                                    |       |

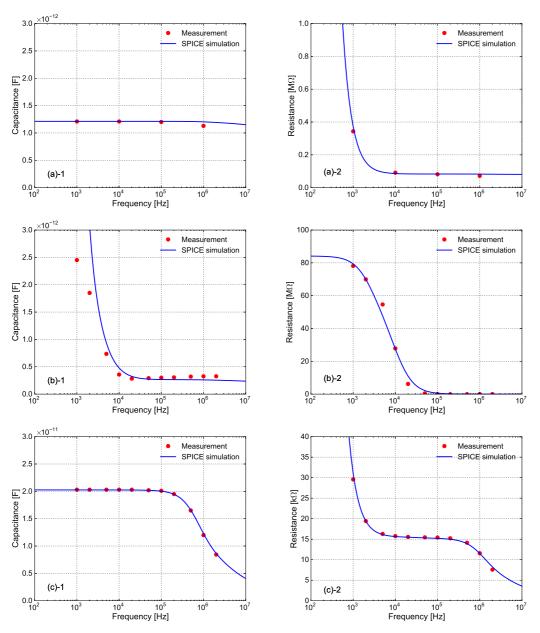

| 13 | .SPICE simulation for $p^+$ n microstrip sensors                                   | 141   |

|    | 13.1. The SPICE model                                                              | . 141 |

|    | 13.2. Results                                                                      | . 143 |

|    | 13.3. Summary and discussion                                                       | . 144 |

|    |                                                                                    |       |

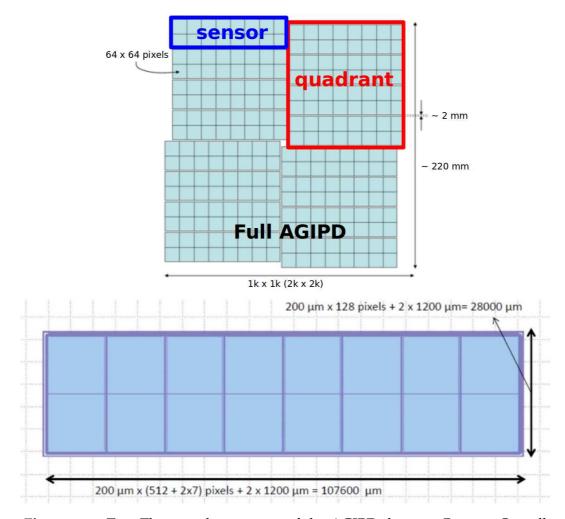

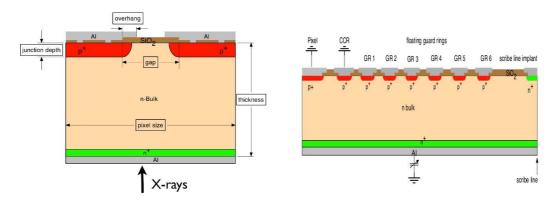

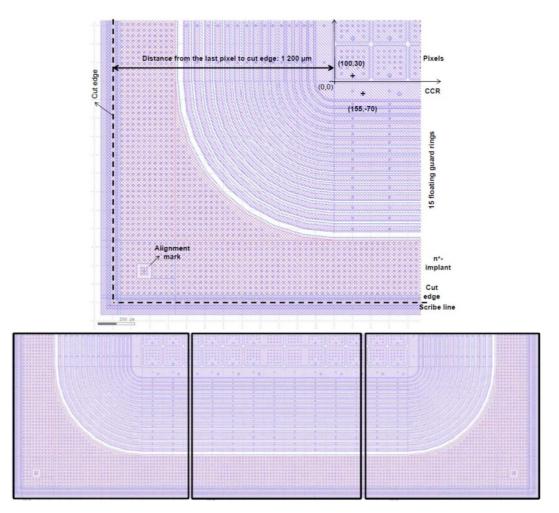

| 14 | . Design of the AGIPD sensor                                                       | 147   |

|    | 14.1. Studies relevant for the AGIPD sensor                                        |       |

|    | 14.2. Specification of the AGIPD sensor                                            |       |

|    | 14.3. Sensor optimization and design of the AGIPD sensor                           |       |

|    | 14.3.1. Sensor optimization                                                        |       |

|    | 14.3.2. Layout of the AGIPD sensor                                                 |       |

|    | 14.4. Summary                                                                      | . 157 |

| 4- |                                                                                    | 4 = 0 |

| 15 | .Summary, conclusions and outlook                                                  | 159   |

|    | 15.1. Summary and conclusions of this thesis                                       |       |

|    | 15.2. Relevance of this study for AGIPD                                            |       |

|    | 15.3. Suggestions for future studies and summary of remaining problems .           | . 161 |

| _  |                                                                                    |       |

| Αp | opendix                                                                            | 163   |

| Α. | Extensive C/G-V, I-V and TDRC measurements                                         | 165   |

|    | A.1. Summary of investigated test structures for dose dependence study .           | . 16  |

|    | A.2. C/G-V, I-V and TDRC of the non-irradiated test fields                         |       |

|    | A 2 C/G-V I-V and TDRC of the irradiated test fields                               | 172   |

# Contents

| A.4. Results of $N_{ox}$ , $N_{it}$ and $J_{surf}$ as function of dose                                                     |              |

|----------------------------------------------------------------------------------------------------------------------------|--------------|

| B. Extensive results of electrical properties of $p^+n$ sensors B.1. Sensor capacitance and resistance versus bias voltage | 1 <b>7</b> 9 |

| C. The mobility of minority carriers at the interface                                                                      | 181          |

| Bibliography                                                                                                               | 183          |

| List of Publications                                                                                                       | 191          |

| Acknowledgments                                                                                                            | 193          |

# List of Figures

| 1.1.         | Bunch structure of XFEL pulses                                             | 1  |

|--------------|----------------------------------------------------------------------------|----|

| 2.1.<br>2.2. | Tedrahedral and crystal structures of silicon atoms                        | 5  |

| 2.2.<br>2.3. | Band structure of silicon atoms                                            |    |

| 2.3.<br>2.4. | The basic bond structures of silicon                                       | 7  |

| 2.5.         | The Fermi level as function of temperature and doping concentration        | ç  |

| 2.6.         | Schematic band diagram, states density, Fermi-Dirac distribution, and etc. | 10 |

| 2.7.         | Generation and recombination processes of carriers                         | 12 |

| 3.1.         | Atomic displacements in the silicon lattice                                | 14 |

| 3.2.         | The energy levels of bulk defects and their effects                        | 15 |

| 3.3.         | Schematic illustration of defects in the $SiO_2$                           | 16 |

| 3.4.         | Schematic illustration of E' center                                        | 17 |

| 3.5.         | Schematic illustration of E', $P_b$ and $P_{bo}$ centers                   | 18 |

| 3.6.         | Mechanisms of formation of oxide charges and interface traps               | 19 |

| 3.7.         | Schematic diagrams of geminate and columnar models                         | 21 |

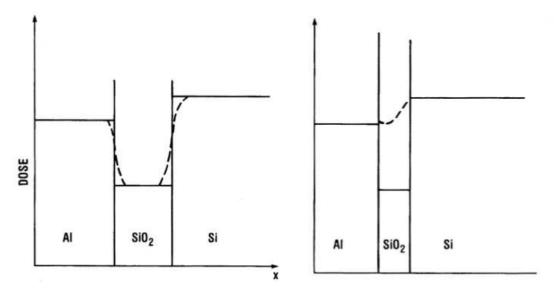

| 3.8.         | Schematic diagram of the dose-enhancement effect                           | 25 |

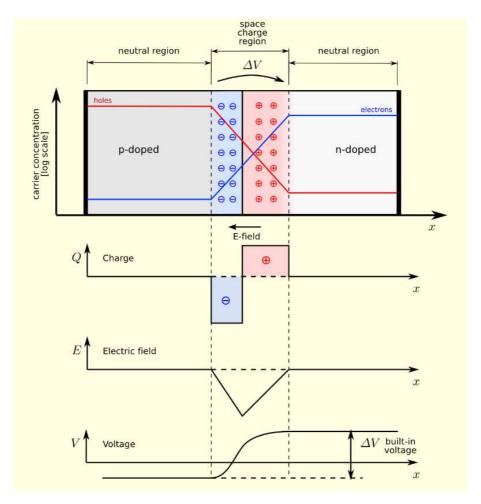

| 4.1.         | Abrupt p on n diode in thermal equilibrium                                 | 32 |

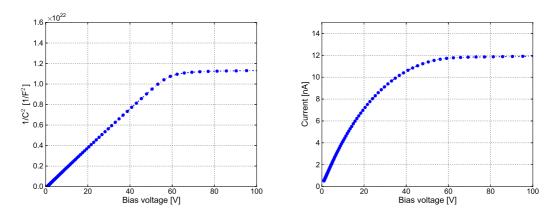

| 4.2.         | C-V and I-V curves of a $p^+n$ pad diode                                   | 34 |

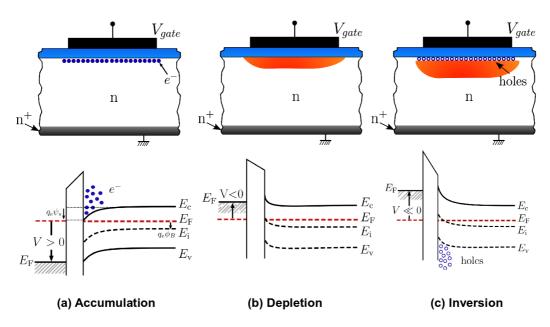

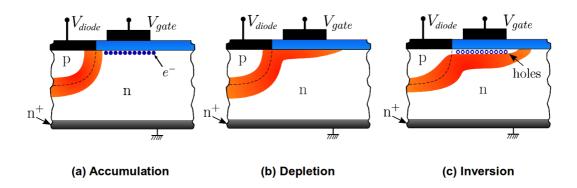

| 4.3.         | Cross section and operating principle of MOS capacitors                    | 35 |

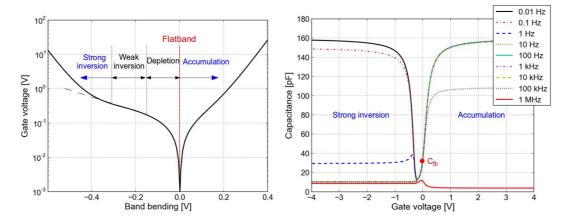

| 4.4.         | Relation between the gate voltage and band bending                         | 37 |

| 4.5.         | Cross section and operating principle of gate-controlled diodes            | 38 |

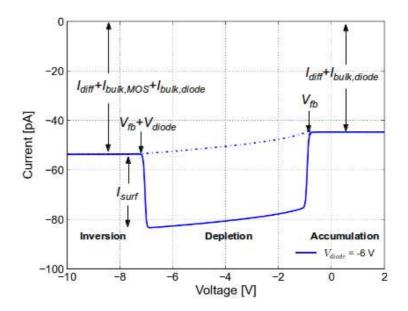

| 4.6.         | Ideal I-V curve of gate-controlled diode                                   | 39 |

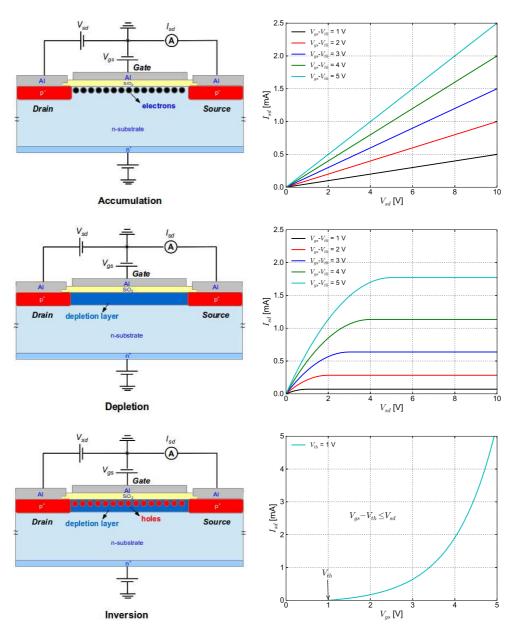

| 4.7.         | Operating principle of p-channel MOSFET                                    | 41 |

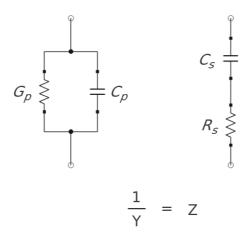

| 5.1.         | The equivalent parallel and series circuits                                | 44 |

| 5.2.         | The principle of the TDRC measurement                                      | 45 |

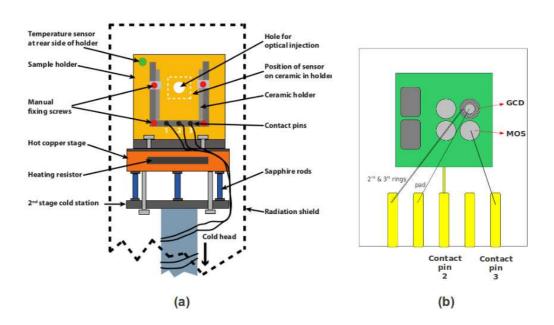

| 5.3.         | The cryostat of the TDRC setup                                             | 47 |

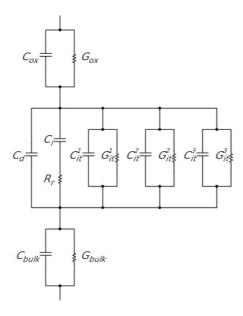

| 6.1.         | Equivalent circuit model of the MOS capacitor                              | 50 |

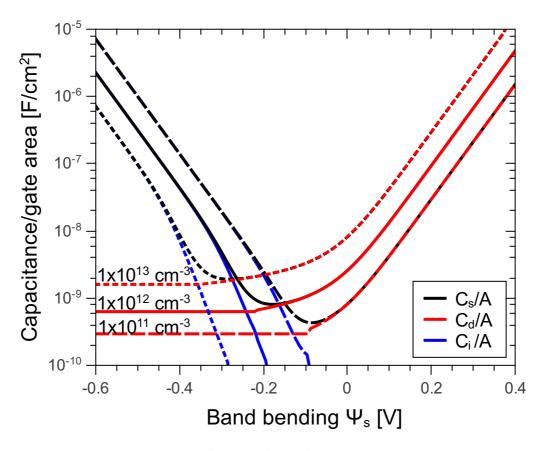

| 6.2.         | Band bending dependence of $C_d$ , $C_i$ and $C_s$                         | 52 |

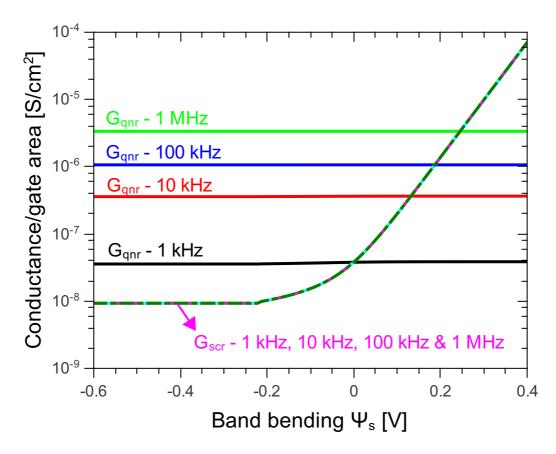

| 6.3.         | Band bending dependence of $G_{qnr}$ and $G_{scr}$                         |    |

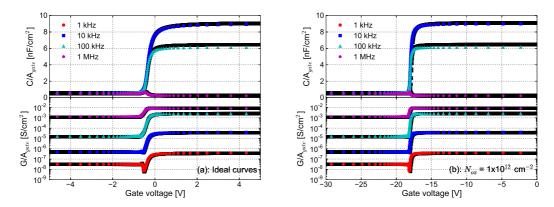

| 6.4.         | C/G-V curves of MOS capacitors without/with oxide charges                  | 58 |

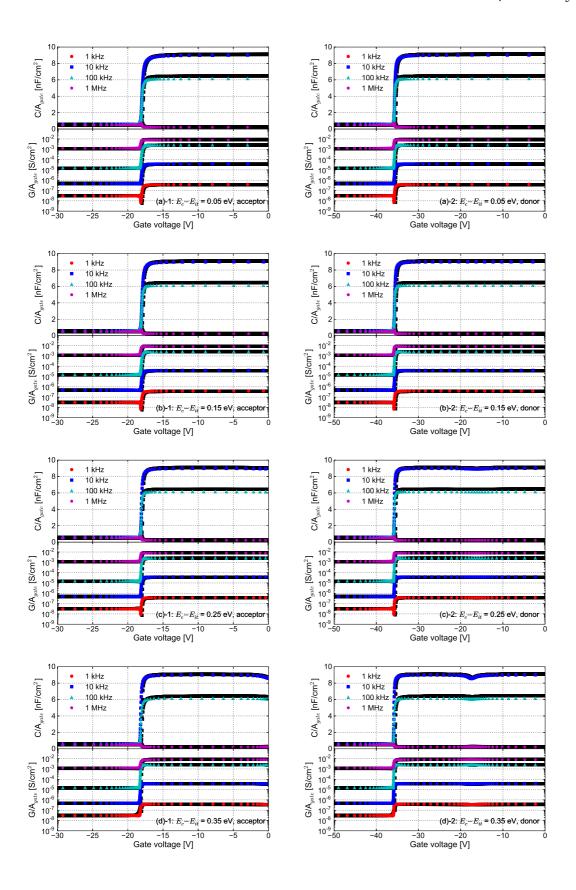

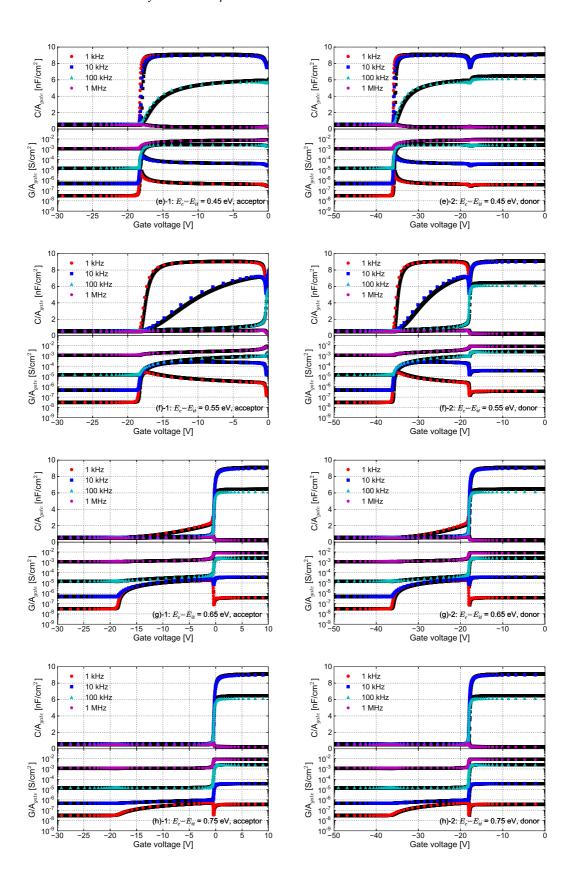

| 6.5.         | C/G-V curves of MOS capacitors with a single interface-trap level          | 63 |

| 6.6.         | C/G-V curves of MOS capacitors with Gaussian distributed interface trap    | 64 |

| 6.7.         | The charge stored in the interface trap                                    | 64 |

| 6.8.         | The capacitances and resistances of a single interface-trap level          | 6- |

# List of Figures

| 6.9.  | The time constants of a single interface-trap level                     | 66          |

|-------|-------------------------------------------------------------------------|-------------|

| 7.1.  | Irradiation facility                                                    | 68          |

| 7.2.  | Front-end of the beam line F <sub>4</sub>                               | 69          |

| 7.3.  | Beam profile                                                            | 70          |

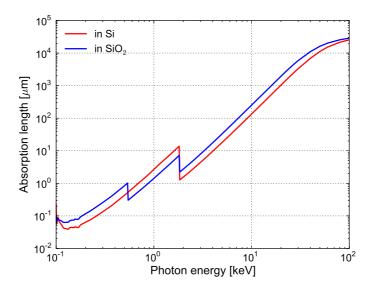

| 7.4.  | Absorption lengths of photons in Si and $SiO_2$                         | 72          |

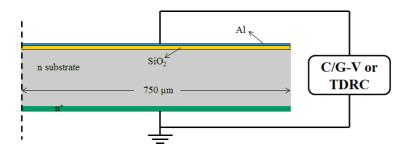

| 8.1.  | Cross section and measurement scheme of a MOS capacitor                 | 75          |

| 8.2.  | Shift of C-V curves due to injection of holes into SiO <sub>2</sub>     | 76          |

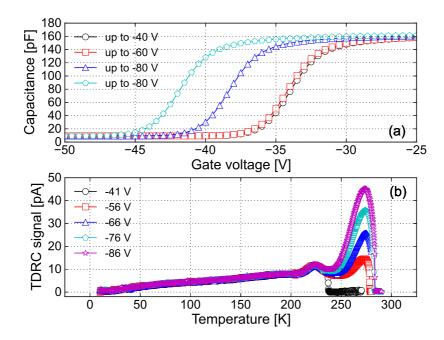

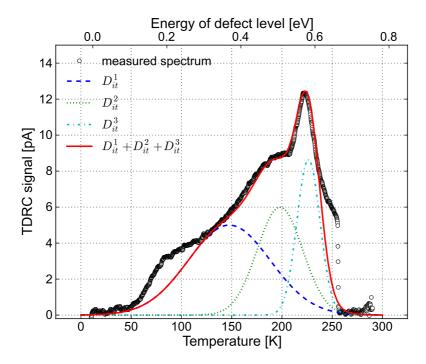

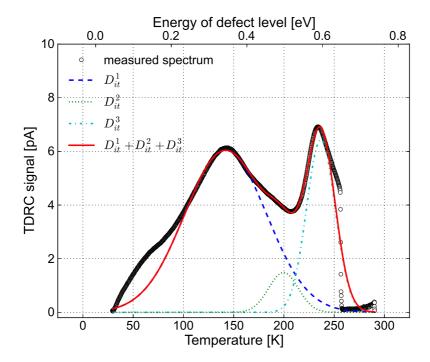

| 8.3.  | TDRC spectrum of a <100> MOS capacitor irradiated to 5 MGy              | 77          |

| 8.4.  | TDRC spectrum of an irradiated MOS capacitor after long-term annealing  | 79          |

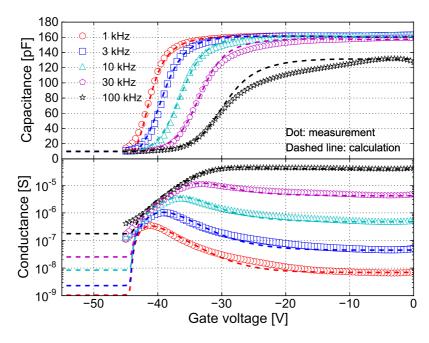

| 8.5.  | Comparison of the measured C/G-V curves to the calculated ones          | 80          |

| 8.6.  | Cross section and measurement scheme of a gate-controlled diode         | 81          |

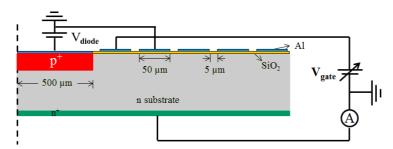

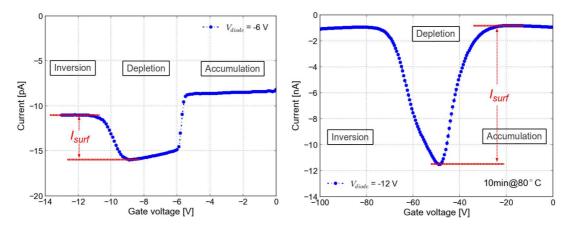

| 8.7.  | Extraction of the surface current                                       | 81          |

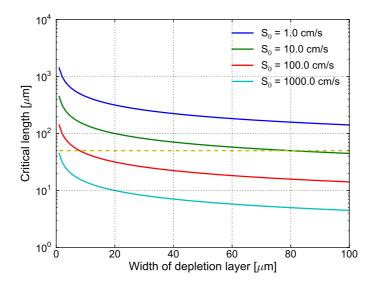

| 8.8.  | Critical length as function of the width of depletion layer             | 83          |

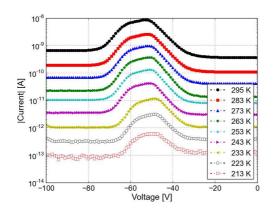

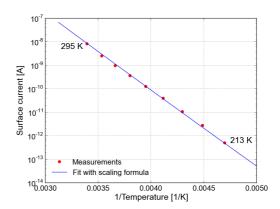

| 8.9.  | Temperature dependence of the surface current                           | 84          |

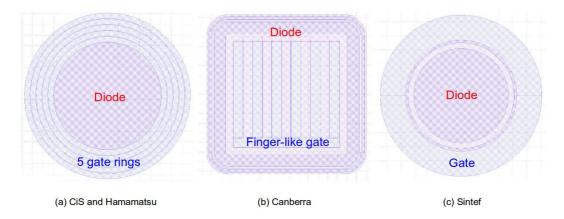

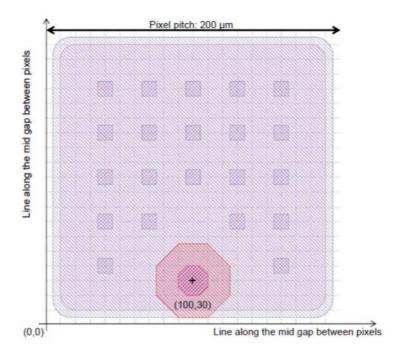

| 9.1.  | Top view of investigated gate-controlled diodes                         | 87          |

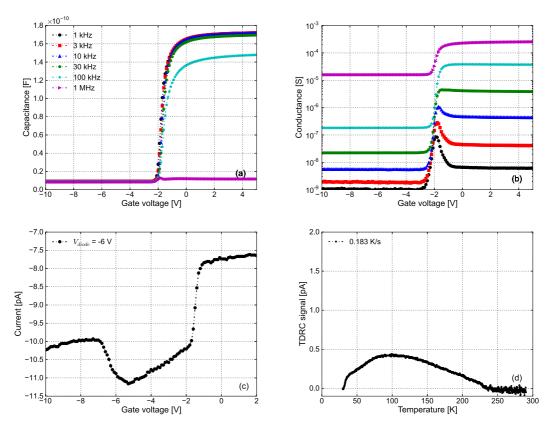

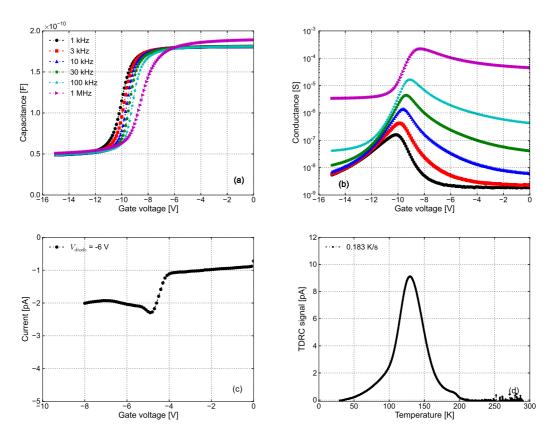

| 9.2.  | C/G-V, I-V and TDRC of the non-irradiated CE2250 fabricated by CiS      | 88          |

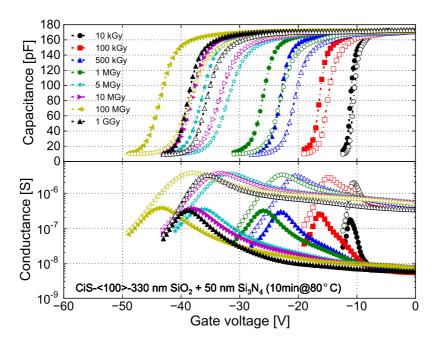

| 9.3.  | Dose dependence of C/G-V curves of CE2250                               | 89          |

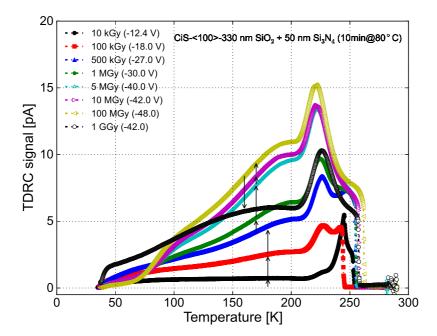

| 9.4.  | Dose dependence of TDRC spectra of CE2250                               | 91          |

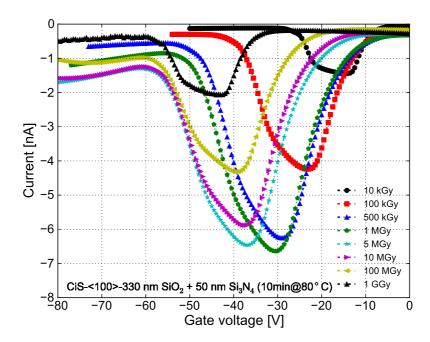

| 9.5.  | Dose dependence of I-V curves of CE2250                                 | 92          |

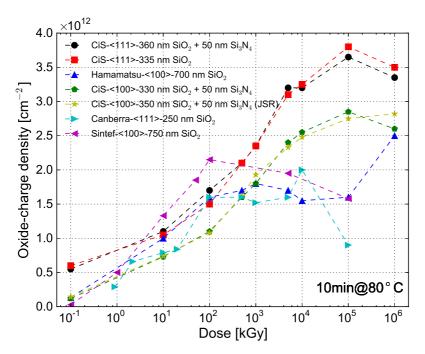

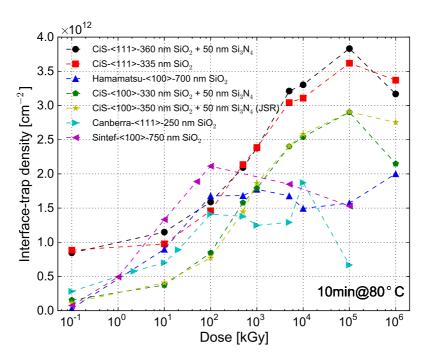

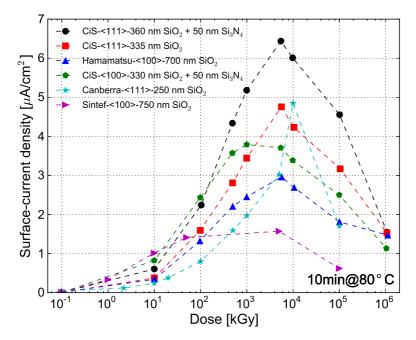

| 9.6.  | Dose dependence of $N_{ox}$ after 10min@80°C annealing                  | 93          |

| 9.7.  | Dose dependence of $N_{it}$ after 10min@80°C annealing                  | 94          |

| 9.8.  | Dose dependence of $J_{surf}$ after 10min@80°C annealing                | 95          |

| 9.9.  | Crystal orientation dependence of C/G-V ant TDRC measurements           | 96          |

| 9.10. | Saturation mechanism of $N_{ox}$                                        | 97          |

| 9.11. | The ratio of $N_{it}/N_{ox}$                                            | 98          |

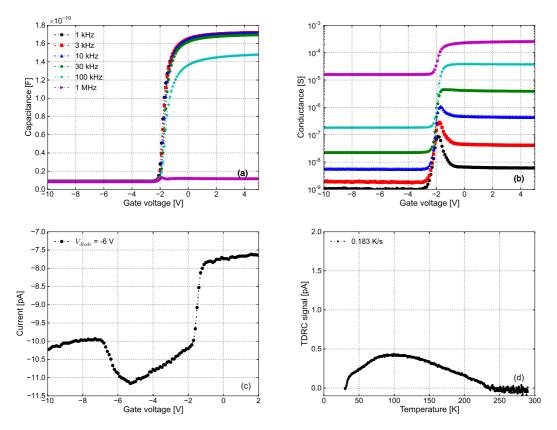

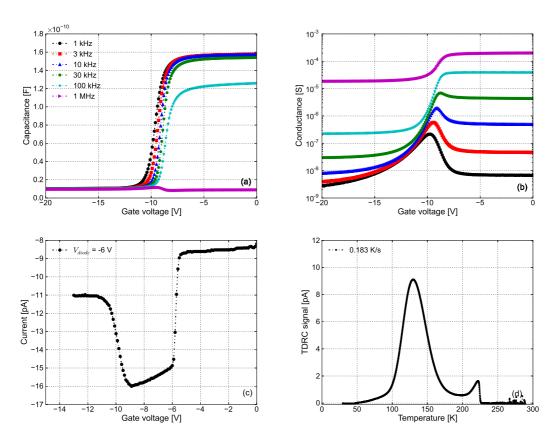

| 10.1. | C/G-V, I-V and TDRC of the non-irradiated test fields                   | 101         |

| 10.2. | C/G-V curves of MOS capacitors                                          | 102         |

| 10.3. | TDRC spectra of MOS capacitors                                          |             |

| 10.4. | I-V curves of MOS capacitors                                            | _           |

| 10.5. | Gate-voltage dependence of $N_{ox}$ , $N_{it}$ and $J_{surf}$           |             |

| 11.1. | Annealing kinectic of $N_{ox}$                                          | 108         |

|       | C/G-V, I-V and TDRC of the non-irradiated test fields                   |             |

| 11.3. | C/G-V curves of MOS capacitors with annealing                           | 113         |

| 11.4. | TDRC spectra of MOS capacitors with annealing                           | 114         |

|       | I-V curves of MOS capacitors with annealing                             |             |

| -     | Annealing of $N_{ox}$ and $J_{surf}$                                    | _           |

|       | Annealing of $N_{ox}$ and $J_{surf}$ extrapolated to other temperatures |             |

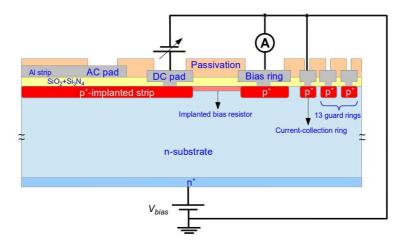

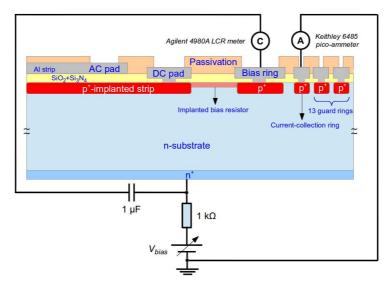

| 12.1. | The AC coupled p <sup>+</sup> n microstrip sensor fabricated by CiS     | <b>12</b> 0 |

|       | The resistance and implantation profile of the bias resistor            |             |

|       | Measurement scheme on the bias resistor                                 |             |

| _     | Measurement scheme for the full depletion voltage                       |             |

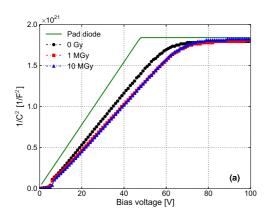

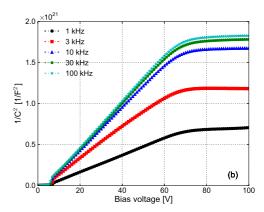

| 12.5.  | The full depletion voltage changes with dose                                 | 124 |

|--------|------------------------------------------------------------------------------|-----|

| 12.6.  | Measurement scheme for the leakage current                                   | 125 |

| 12.7.  | The leakage current                                                          |     |

| 12.8.  | The electron-accumulation layer in the CiS microstrip sensor                 | 127 |

| 12.9.  | Measurement scheme for the interstrip capacitance                            | 128 |

| 12.10. | The interstrip capacitance changes with bias voltage, dose and frequency     | 129 |

| 12.11. |                                                                              | 129 |

|        | The interstrip resistance of the non-irradiated microstrip sensor            | 130 |

| 12.13. | Defined notations for the AC coupled microstrip sensor                       | 130 |

| 12.14. | The interstrip resistance of the irradiated microstrip sensor                | 132 |

| 12.15. | . Measurement scheme for the coupling capacitance                            | 134 |

| 12.16. | The coupling impedance as function of frequency                              | 134 |

| 12.17. | The RC circuit for the coupling impedance measurement                        | 135 |

| 12.18. | The full depletion voltage changes with irradiation condition                | 136 |

| 12.19. | . The leakage current and CCR current change with irradiation condition .    | 137 |

| 12.20. | The interstrip capacitance changes with irradiation condition                | 138 |

|        | CDICE and delication AC annual darks and action and a                        |     |

|        | SPICE model for the AC coupled p <sup>+</sup> n microstrip sensor            |     |

| 13.2.  | Comparison of SPICE simulation and measurements                              | 145 |

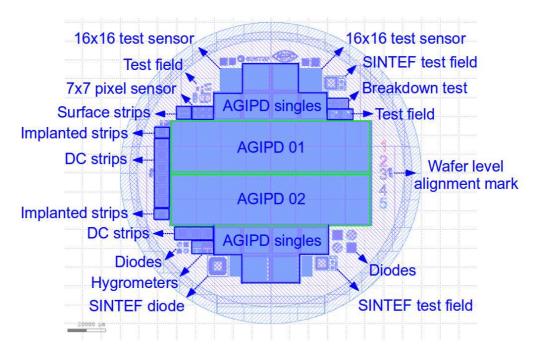

| 14.1.  | Overall layout and dimensions of an AGIPD sensor                             | 150 |

| 14.2.  | Sketch of the sensor region simulated for sensor optimization                |     |

| 14.3.  | Layout and dimensions of the guard-ring structure                            |     |

| 14.4.  | Layout and dimensions of the standard 200 $\mu$ m $\times$ 200 $\mu$ m pixel |     |

| 14.5.  | Layout of the AGIPD wafer                                                    |     |

|        |                                                                              |     |

| A.1.   | Measurements on the non-irradiated CE2250                                    |     |

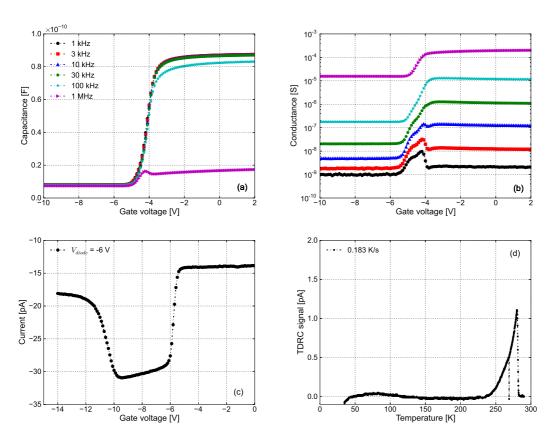

| A.2.   | C/G-V, I-V and TDRC of the non-irradiated CBo <sub>45</sub> o                |     |

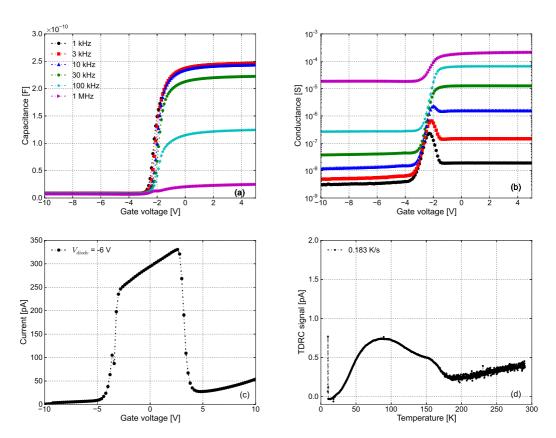

| A.3.   | C/G-V, I-V and TDRC of the non-irradiated 6336-01-03                         |     |

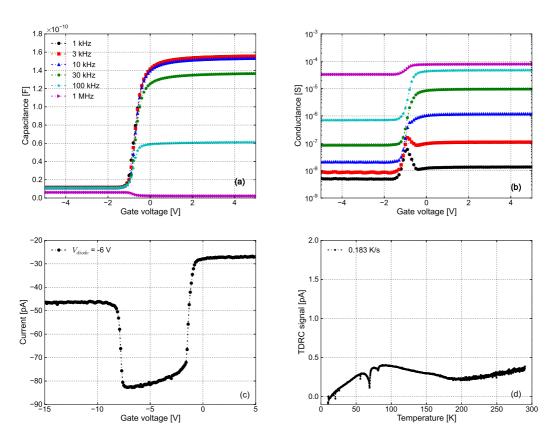

| A.4.   | C/G-V, I-V and TDRC of the non-irradiated HAMA-04                            |     |

| A.5.   | C/G-V, I-V and TDRC of the non-irradiated Canberra-145/7                     |     |

| A.6.   | C/G-V, I-V and TDRC of the non-irradiated Sintef-1/2/3                       |     |

| A.7.   | Dose dependence of C/G-V curves                                              |     |

| A.8.   | Dose dependence of TDRC spectra                                              | 173 |

| A.9.   | Dose dependence of I-V curves                                                |     |

| A.10.  | Dose dependence of $N_{ox}$ and $J_{surf}$ before annealing                  | 177 |

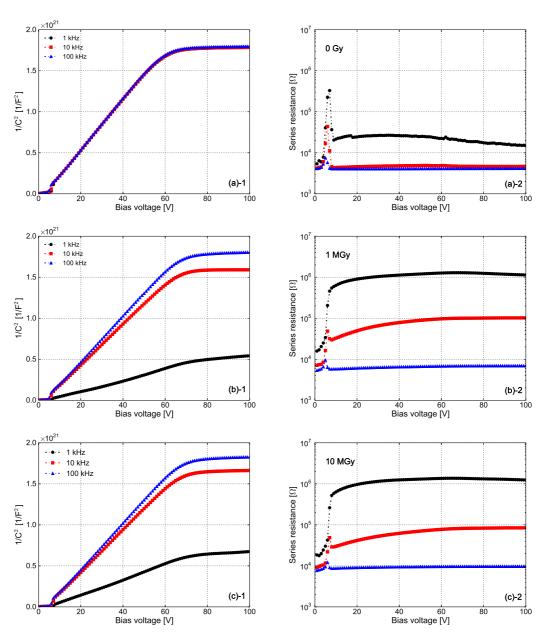

| B.1.   | The total sensor capacitance and series resistance                           | 180 |

| C.1.   | The mobility of minority carriers at the interface                           | 181 |

# List of Tables

| 1.1.           | Parameters of the AGIPD, LPD and DSSC                                         | 2          |

|----------------|-------------------------------------------------------------------------------|------------|

| 3.1.           | Description of symbols in the equations (3.17)-(3.19)                         | 23         |

|                | Symbols in the model of the MOS capacitor                                     | 50<br>57   |

| 8.1.           | Properties of the three dominant interface-trap levels                        | 78         |

| 9.1.           | List of investigated test fields in the study of dose dependence              | 86         |

| 10.1.          | Properties of the test fields used for the study of gate-voltage dependence . | 100        |

| 11.2.          | Properties of the test fields used for annealing study                        | 116        |

| 12.2.<br>12.3. | The effective doping concentration of the CiS microstrip sensors              | 132<br>133 |

| 13.1.<br>13.2. | Symbols in SPICE model                                                        | 142<br>143 |

| 14.1.          | The specifications of the AGIPD sensor                                        | 149        |

| A.2.           | Summary of the parameters of investigated test structures                     | 175        |

| A.4.<br>A.5.   | Dose dependence of $N_{ox}$ , $N_{it}$ and $J_{surf}$ for Sintef-1/2/3        | 175<br>176 |

|                | Dose dependence of $N_{ox}$ , $N_{it}$ and $J_{surf}$ for Canberra-145/7      |            |

# 1. Introduction

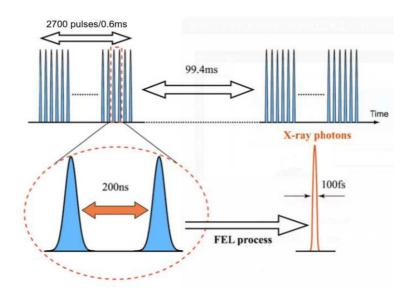

The next generation light source, the European X-ray Free Electron Laser (XFEL) [1], is now being constructed at DESY, Hamburg and its commissioning is scheduled for 2015. The European XFEL will deliver 27,000 fully coherent, high brilliance X-ray pulses per second each with a duration below 100 fs (as seen in figure 1.1). Studies will be performed in physics, chemistry, life science, materials research and other disciplines with X-ray beam of unique quality. Some unique applications include the structural analysis of single complex organic molecules, the investigation of chemical reactions at the femtosecond-time scale and the study of processes that occur in the interior of planets.

**Figure 1.1**: The bunch structure of X-ray pulses at the European XFEL: The bunch trains with up to 2700 X-ray pulses, each of a duration of less than 100 femtosecond and separated by 220 ns, repeated 10 times per second.

At the European XFEL, silicon pixel detectors will be used for imaging experiments. They must meet the following extraordinary requirements [2]:

- Large energy range of photons from 0.5 keV to 24 keV

- Sensitivity of single-photon detection

- A dynamic range of up to more than 10<sup>4</sup> 12.4 keV photons per pixel per bunch

- A frame rate of 4.5 MHz to satisfy the high repetition rate of X-ray pulses

- Radiation tolerance of 1 GGy (sensor) and 100 MGy (ASIC) for 3 years of operation

# 1.1. The detector projects for the XFEL: AGIPD, LPD and DSSC

There are three ongoing projects of 2-dimensional imaging detectors for the European XFEL: the Adaptive Gain Integrating Pixel Detector (AGIPD), the Large Pixel Detector (LPD), and the DEPFET (Depleted P-Channel Field Effect Transistor) Sensor with Signal Compression (DSSC).

All the three detectors have to deal with single photon detection and at the same time 10<sup>4</sup> ph/pixel/bunch simultaneously. However, the solutions taken by the three detectors are different: For AGIPD, a dynamic gain switching circuit is designed in ASIC, whose gain can be automatically switched according to the charge produced by the photons. For LPD, three parallel amplifier stages are designed, and the appropriate one can be chosen. For DSSC, its sensor has an intrinsic non-linear gain.

| The frontend | parameters | of the AGIPD | , LPD and | DSSC are | give in t | able 1.1 [ˈ | 3-5]. |

|--------------|------------|--------------|-----------|----------|-----------|-------------|-------|

|              |            |              |           |          |           |             |       |

| Parameter                 | AGIPD                             | LPD                              | DSSC                              |

|---------------------------|-----------------------------------|----------------------------------|-----------------------------------|

| technology                | silicon                           | silicon                          | silicon, DEPMOS                   |

| energy range              | [3 keV, 24 keV]                   | [1 keV, 24 keV]                  | [0.5 keV, 24 keV]                 |

| pixel size                | $200 \times 200 \ \mu \text{m}^2$ | $500 \times 500 \ \mu\text{m}^2$ | $204 \times 236 \ \mu \text{m}^2$ |

| single photon sensitivity | yes                               | yes                              | yes                               |

| soft X-ray detection      | no                                | no                               | yes                               |

| dynamic range             | $2 \times 10^4$                   | $10^{5}$                         | $\sim 10^4$                       |

| frame rate                | 4.5 MHz                           | 4.5 MHz                          | 4.5 MHz                           |

| storage cells             | 352                               | 512                              | 640                               |

| ADC gain control          | switched 1 fold                   | 3 fold                           | non-linear                        |

**Table 1.1**: Parameters of the AGIPD, LPD and DSSC detectors.

#### 1.2. Motivation and structure of this thesis

To address the fore-mentioned challenges, in particular the question of radiation tolerance of 1 GGy in silicon sensor, a good understanding of radiation damage caused by X-rays is required.

The aim of this thesis is to

- understand the radiation damage induced by X-rays,

- extract the damage-related parameters, i.e. the oxide-charge density and the surface-current density, which are the main inputs for sensor optimization with Technology Computer Aided Design (TCAD) [6] simulation,

- investigate the effects due to the voltage applied to the gates of the MOS capacitor and the gate-controlled diode during irradiation,

- verify the long-term stability and performance of silicon sensors with the help of annealing studies,

- investigate the influence of X-ray irradiations on the electrical properties of segmented sensors, and

- design a radiation-hard silicon pixel sensor for the AGIPD Project according to the optimized layout as a result of TCAD simulations.

For the investigation of X-ray radiation damage up to 1 GGy, MOS capacitors and gate-controlled diodes built on high resistivity n-doped silicon with crystal orientations <100> and <111> produced by four vendors, CiS, Hamamatsu, Canberra and Sintef, have been irradiated with 12 keV X-rays at the DESY DORIS III synchrotron light source. The irradiation facility is introduced in chapter 7. Using solid-state measurements, together with model calculation, the oxide-charge density, the interface-trap density and the surface-current density have been determined as function of dose. The measurement set-ups and principles are introduced in chapter 5, the model calculation in chapter 6, the extraction methods in chapter 8, and the results shown in chapter 9.

In addition, the influence of the voltage applied to the gates of the MOS capacitor and the gate-controlled diode during X-ray irradiation on the oxide-charge density, the interface-trap density and the surface-current density has been investigated at doses of 100 kGy and 100 MGy. The results are presented in chapter 10.

To understand the long-term stability of irradiated sensors, annealing studies have also been performed at  $60\,^{\circ}\text{C}$  and  $80\,^{\circ}\text{C}$  on MOS capacitors and gate-controlled diodes irradiated to 5 MGy and the annealing kinetics of oxide charges and surface current determined and given in chapter 11.

The macroscopic electrical properties of segmented  $p^+n$  sensors as function of X-ray dose have been also investigated and results are presented in chapter 12.

Finally, chapter 14 shortly summarizes the efforts by the detector group of Hamburg University for an optimized radiation-hard silicon pixel sensor for the AGIPD Project, and the optimized sensor layout according to the results of TCAD simulation with damage-related parameters.

# 2. Properties of silicon crystals

The physics of silicon devices is naturally dependent on the physics of silicon crystals. The chapter presents a short introduction to the basic physics and properties of silicon.

# 2.1. Crystal structure of Si

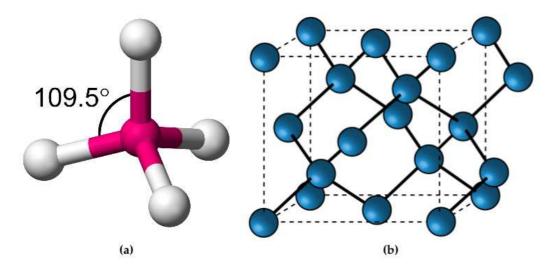

Silicon crystals have a well-structured periodic placement of silicon atoms. The smallest assembly of silicon atoms is called a primitive cell, whose dimension is characterized by the lattice constant a (a = 0.543 nm at 300 K). The primitive cell is repeated to form the entire silicon crystal.

The silicon crystal has a diamond lattice structure. Such a structure belongs to the tetrahedral phases, in which each silicon atom is surrounded by four neighbouring atoms sharing covalent bonds (figure 2.1(a)). Figure 2.1(b) shows the crystal structure of silicon in face-centred cubic orientation.

**Figure 2.1**: (a) Tedrahedral structure of silicon atoms with four neighbouring atoms sharing covalent bonds. (b) Crystal structure of silicon in face-centred cubic orientation. Picture taken from [7].

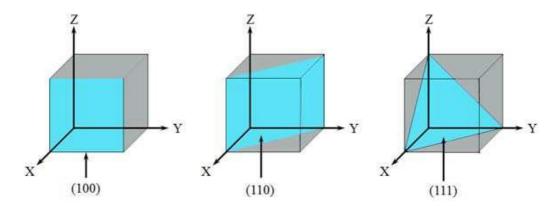

The orientations and properties of the planes of crystal surface are important. A method to characterize the orientation of planes in a crystal is to use Miller indices: The indices are determined by first finding the intercepts of the plane with the three axe in a (x,y,z) coordinate system in terms of primitive cells, and then taking the reciprocals of these numbers and reducing them to the smallest integers having the

same ratio [8]. The result is enclosed in parentheses (*hkl*) called the Miller indices for a single plane or a set of parallel planes *hkl*. Figure 2.2 shows the Miller indices of important planes in a cubic crystal.

**Figure 2.2**: Miller indices of some important planes in a cubic crystal. Picture taken from [8].

#### 2.2. Band structure of silicon

Semiconductors like silicon have unique electric conductive properties, which are related to the energy difference between the valence and conduction band. The energy difference is called *band gap*. Compared to metals and insulators, semiconductors have an intermediate level of electric conductivity at room temperature. The band gap of a semiconductor is so small that a slight increase of temperature promotes sufficient electrons from the lowest energy level in the valence band to the conduction band. However, the band gap of an insulator is normally large (> 4 eV) so that it dose not allow for electron motion. For metals, their conduction and valence bands overlap, thus electrons can move quite freely between energy levels without a high energy cost.

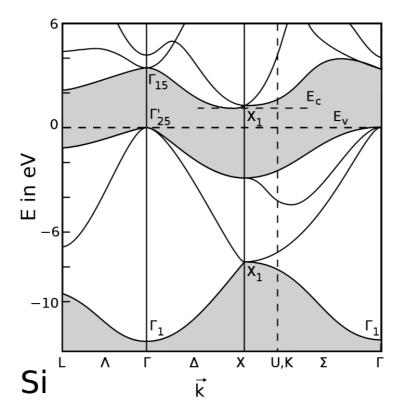

The band structure of silicon is shown in figure 2.3. Silicon has a so-called indirect band gap ( $E_g = 1.12$  eV at 300 K), which is the (minimum) energy difference between the lower edge of the conduction band and the upper edge of the valence band at different momenta **k** of the electrons.

#### 2.3. Intrinsic and non-intrinsic silicon

A silicon without any dopant is defined as an intrinsic silicon. The numbers of electrons occupied conduction-band levels and holes occupied valence-band levels in an intrinsic silicon crystal are the same and they equal to the intrinsic carrier density at thermal equilibrium condition. The intrinsic carrier density  $n_i$  depends on the effective densities of states in the conduction and valence bands,  $N_c$  and  $N_v$ , temperature, T, and silicon band gap,  $E_g$ :  $n_i = \sqrt{N_c N_v} \exp(-E_g/(2k_BT))$ , with  $k_B$  the Boltzmann constant.

**Figure 2.3**: Band structure of silicon at a temperature of 300 K. The energy difference between the lower edge of the conduction band (close to X) and the upper edge of the valence band (at  $\Gamma$ ) is 1.12 eV. X and  $\Gamma$  are the particular directions/points of the wave vector within the Brillouin Zone (BZ) corresponding to the crystal lattice of silicon. Picture reproduced from [7].

#### 2. Properties of silicon crystals

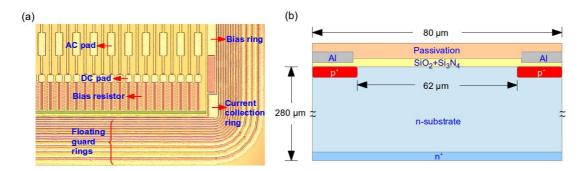

One of the most important properties of silicon is that it can be doped with different types and concentrations of impurities to change its resistivity. In addition, when these impurities are ionized and the carriers are depleted, they leave a charged region which results in an electric field and sometimes a potential barrier inside the doped silicon. The mostly used dopants in silicon sensors are phosphorus and boron. The doped atoms of phosphorus or boron in silicon replace silicon atoms in the lattice and results in an excess of electrons or holes.

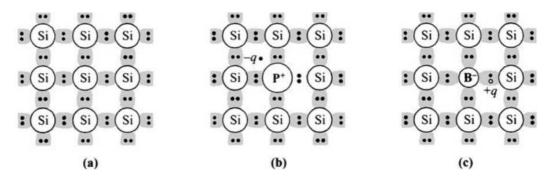

Figure 2.4 shows three basic bond pictures of silicon. (a) Intrinsic silicon, which is pure and contains no impurities. Each silicon shares its four valence electrons with the four neighbouring silicon atoms, which forms four covalent bonds. (b) n-type silicon (phosphorus as dopant), where a phosphorous atom with five valence electrons replaces a silicon atom and leaves an electron donated to the lattice in the conduction band. The dopant, which is able to produce excess electrons, is called *donor*. (c) p-type silicon (boron as dopant), where a boron atom with three valence electrons replaces a silicon atom in the lattice and leaves a hole created in the valence band. The dopant producing excess holes is called *acceptor*.

**Figure 2.4**: Three basic bond pictures of silicon. (a) Intrinsic Si without impurities. (b) n-type Si with donor (phosphorus). (c) p-type Si with acceptor (boron). Picture taken from [8].

For n-type silicon, the number of electrons in the conduction band is given by the effective density of states in the conduction band  $N_c$  and the Fermi energy level  $E_F$ ,

$$n = N_c \exp\left(-\frac{E_c - E_F}{k_B T}\right) \tag{2.1}$$

with  $E_c$  the energy of conduction band. Similarly, for a p-type silicon, the number of holes in the valence band can be written as

$$p = N_v \exp\left(-\frac{E_F - E_v}{k_B T}\right) \tag{2.2}$$

where  $E_v$  is the energy of valence band. For an intrinsic silicon, due to the fact that  $n = p = n_i$ , the Fermi energy level is given by

$$E_F = E_i = \frac{E_c + E_v}{2} + \frac{k_B T}{2} \ln\left(\frac{N_v}{N_c}\right)$$

(2.3)

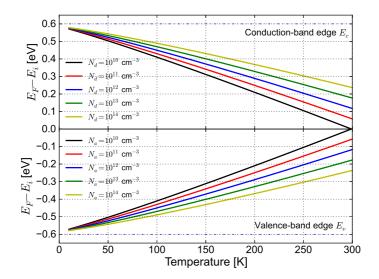

Hence the intrinsic Fermi level  $E_i$  of a silicon is located very close to the middle of the band gap. However, the Fermi levels  $E_F$  of an n-type silicon and a p-type silicon lie in the upper half and the lower half of the band gap, respectively. Figure 2.5 shows the Fermi level  $E_F$  as function of temperature T and doping concentration ( $N_d$  for n-type silicon;  $N_a$  for p-type silicon). At low temperature, the Fermi level  $E_F$  moves to the band edge of silicon.

**Figure 2.5**: The Fermi level  $E_F$  as function of temperature T and doping concentration ( $N_d$  for n-type silicon;  $N_a$  for p-type silicon). The conduction-band edge  $E_c$  and valence-band edge  $E_v$ , which are taken from the values at  $\sim$  0 K, are shown here for eye-guidance.

The occupation of conduction-band levels, valence-band levels and defects levels in the forbidden band of silicon is a strong function of temperature and energy, and is determined in equilibrium condition ( $pn = n_i^2$ ) by the Fermi-Dirac distribution function

$$F(E) = \frac{1}{1 + \exp\left(\frac{E - E_F}{k_B T}\right)} \tag{2.4}$$

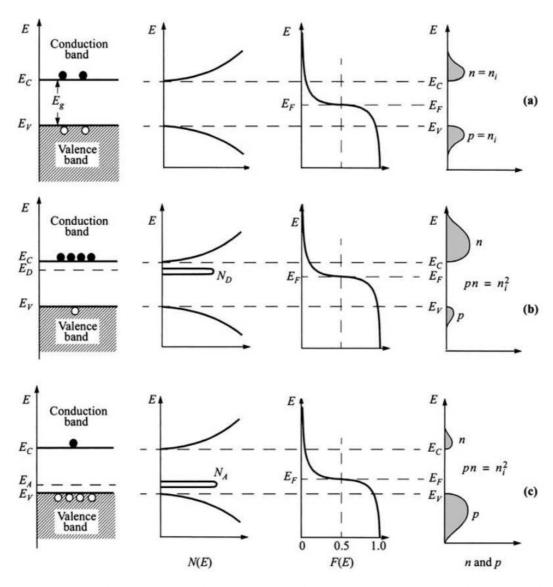

Figure 2.6 shows the schematic band diagram, states density, Fermi-Dirac distribution and carrier concentrations in the conduction band and valence band for intrinsic, n-type and p-type silicon at thermal equilibrium condition.

## 2.4. Transport of carriers

When an electric field exists in a silicon crystal, holes can drift in the direction of the electric field and electrons in the opposite direction. The drift of carriers inside a silicon causes a current. The drift current under an electric field is given by

**Figure 2.6**: Schematic band diagram, states density, Fermi-Dirac distribution, and carrier concentration for (a) intrinsic, (b) n-type, and (c) p-type silicon at thermal equilibrium. Picture taken from [8].

$$\vec{\mathbf{J}} = \sigma \vec{\mathbf{E}} \tag{2.5}$$

where  $\sigma$  is the conductivity,

$$\sigma = \frac{1}{\rho} = q_0 \left( \mu_n n + \mu_p p \right) \tag{2.6}$$

and  $\rho$  is the resistivity of the silicon material.  $\mu_n$  and  $\mu_p$  are the mobilities of electrons and holes in silicon (unit: cm<sup>2</sup>/(V·s)). The mobilities of electrons and holes depend on the electric field and their values saturate at higher field. For an n-type silicon, due to  $n \gg p$ , the conductivity is given by  $\sigma = q_0 \mu_n n$ .

In the electric field, carriers drift with a velocity. The drift velocity can be written as

$$\vec{\mathbf{v}}_{\mathbf{d}} = \pm \mu(E)\vec{\mathbf{E}} \tag{2.7}$$

with "+" for holes and "-" for electrons.

In addition, carriers undergo a random diffusion in silicon due to their thermal energy. One important parameter related to the diffusion is the diffusion length of carriers in silicon, which is a direct reflection of diffusion current. The diffusion length L depends on the diffusion coefficient of carriers D and their lifetime  $\tau$ :  $L = \sqrt{D\tau}$ , with  $D = \mu k_B T/q_0$  the Einstein relation. The larger the diffusion length, the smaller the diffusion current in silicon.

#### 2.5. Generation and recombination of carriers

When the thermal-equilibrium condition of a silicon is changed (i.e.,  $pn \neq n_i^2$ ), recombination or thermal generation process restores the system to equilibrium (i.e.,  $pn = n_i^2$ ).

One recombination process is the band-to-band direct electron-hole recombination: Electrons jump from the conduction band to the valence band with a photon emitted (radiative process) or with energy transferred to another free carrier (Auger process). Another important recombination process is indirect recombination of electrons and holes with the help of defect levels in the forbidden band gap of silicon. Those defects in silicon not only change the electrical properties of silicon but also influence the lifetime of carriers.

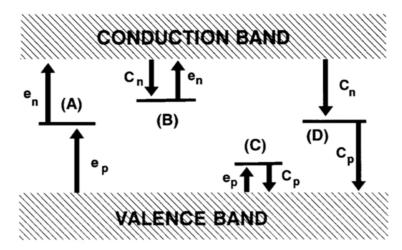

The defect levels in the forbidden band gap of silicon are able to capture electrons and holes. The capture rates are denoted as  $c_n$  and  $c_p$ . They can also emit the captured electrons and holes to the conduction and valence bands, respectively. The emission rates are denoted as  $e_n$  and  $e_p$ . The processes that a defect emits/captures a hole to/from the valence band are equivalent to that a defect captures/emits an electron from/to the valence band. Figure 2.7(A) and (D) are the generation and recombination processes of carriers through the defect level. Figure 2.7(B) shows the electron-capture and -emission processes through a defect level in the upper half of the band gap; figure 2.7(C) shows the hole-capture and -emission processes through a defect level in the lower half of the band gap.

#### 2. Properties of silicon crystals

**Figure 2.7**: Generation and recombination processes of carriers: Generation (A), electron trapping (B), hole trapping (C) and recombination (D).

For a generation/recombination centre, the steady-state condition is that the difference between the capture and emission rates of electrons  $(c_n - e_n)$  equal to  $(c_p - e_p)$  for holes. Hence, the recombination rate of non-equilibrium carriers  $U: U = c_n - e_n = c_p - e_p$ . It can be described by the Shockley-Read-Hall statistics as [8]

$$U = \frac{\sigma_n \sigma_p v_{th} N_t \left( pn - n_i^2 \right)}{\sigma_n \left[ n + n_i \exp\left(\frac{E_t - E_i}{k_B T}\right) \right] + \sigma_p \left[ p + n_i \exp\left(\frac{E_i - E_t}{k_B T}\right) \right]}$$

(2.8)

where  $\sigma_n$  and  $\sigma_p$  are the electron- and hole-capture cross sections,  $E_t$  and  $N_t$  the energy level and density of defects, and  $v_{th}$  the thermal velocity of free carriers.

The generation/recombination of non-equilibrium carriers causes leakage current in case they are exposed to an electric field. According to equation (2.7), it is seen that the recombination rate U is very sensitive to the energy level of defects and its peak value appears at  $E_t = E_i$  for  $\sigma_n/\sigma_p = 1$ . Hence, the leakage current caused by defect levels is a direct reflection of defect density at the middle of silicon band gap in this situation.

# 3. Radiation damage induced by X-rays

Silicon detectors are used in nuclear and particle physics since 1960s. However, the real breakthrough came in the early 1980s when micrometer position resolution for charged particles has been achieved and their superior performance for tracking down short-lived particles in experiments of particle physics demonstrated. Since then silicon detectors also found many applications outside of particle physics. Most prominent are the applications of silicon pixel detectors for X-rays in astronomy and at synchrotron radiation sources. New accelerators, in particular the High Luminosity Large Hadron Collider (HL-LHC) and the European X-ray Free Electron Laser, will lead to much higher beam intensities and result in radiation damage in silicon sensors and electronics. The high dose radiation in silicon sensors damages the silicon crystal and its insulating layer, which changes the sensor properties and shorten their lifetime.

This chapter introduces the radiation effects and gives a general understanding of radiation damage, especially the mechanism, microscopic and macroscopic effects of radiation damage induced by X-rays.

# 3.1. Bulk and surface damage

There are two kinds of radiation damage: bulk damage and surface damage. The former is due to the non-ionizing energy loss (NIEL) [9] of incident particles, i.e. protons, neutrons, electrons and gamma-rays, which cause silicon crystal damage; the latter is due to the ionizing energy loss of charged particles or X-ray photons, which causes the build-up of positive charges and traps in the SiO<sub>2</sub> and at the Si-SiO<sub>2</sub> interface.

#### Bulk damage

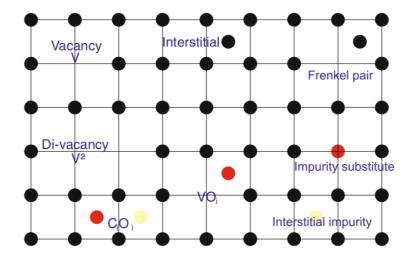

Hadrons, electrons and gamma-rays interact with the silicon atoms via the electromagnetic and strong forces. The silicon atoms can be displaced and create interstitials I and vacancies V. In addition, some more complex configurations, for example di-vacancies  $V_2$  and triple-vacancies  $V_3$ , can be created. Figure 3.1 is an exemplary selection of atomic displacements in the silicon lattice after collision with incident particles.

The bulk defects can be classified as point defects and defect clusters. The point defects are so-called *Frenkel-pairs*, which simply consist of a pair of vacancy and interstitial. The defect clusters are dense agglomerations of defects, which usually form at the end of a track of the non-ionizing interaction/collision. The minimum recoil energy of a silicon atom ( $E_{rec}^{Si}$ ) to produce point defects is 25 eV. Both point defects

**Figure 3.1**: An exemplary selection of atomic displacements in the silicon lattice caused by the interactions of incidence particles [10]. V - vacanies; I - interstitials;  $V_2$  - di-vacancies;  $VO_i$  - combination of vacancies and oxygen interstitials;  $C_iO_i$  - combination of carbon and oxygen interstitials. Picture taken from [10].

and defect clusters can be produced for  $E_{Si}^{rec} > 5$  keV [9]. The point defects can be caused by gamma-rays and low energy electrons ( $E_e < 1$  MeV), and the defect clusters caused by high energy electrons ( $E_e > 8$  MeV) and hadrons.

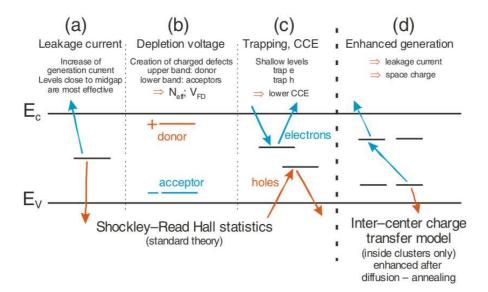

As seen in figure 3.2, the defects in silicon crystal change the following properties of silicon sensors:

- increase of leakage current

- change of full depletion voltage

- change of effective doping concentration

- change of trapping time

- decrease of charge-collection efficiency

The bulk defects and their influence on the electrical properties of silicon sensors for experiments at the LHC have been studied extensively and can be found elsewhere [9,12–14].

#### Surface damage

Radiations by X-rays, gamma-rays and charged particles, e.g. electrons and protons, ionize the Si atoms of crystal and the molecules in the insulating layer, which covers the silicon crystal. Typically, the average ionization energy to produce an electronhole pair is 3.6 eV for silicon and 17 eV for SiO<sub>2</sub>. The carriers produced by ionizing radiation in silicon can be collected by the electrodes. However for the carriers in the insulating layer, some of them cannot escape from this layer, and those remaining form permanent charges in the insulating layer and traps at the interface between silicon and the insulating layer. Hence, the ionizing radiation only damages the in-

**Figure 3.2**: The energy levels of bulk defects and their effects. (a) Energy levels close to the mid-gap of silicon are responsible for the generation of leakage current. In addition to high leakage current, levels around the mid-gap of silicon with high states density change the electric field in silicon bulk and further cause the double junction effect [11]. (b) Donors and acceptors in the upper half and lower half of the band gap change the effective doping concentration. (c) Shallow levels trap electrons and holes, and further reduce the charge-collection efficiency (CCE). (d) The inter-center charge transfer model indicates the combination of different defects in the defect clusters and further enhance the effects. Figure taken from [10].

sulting layer and the interface between the insulating layer and the silicon.  $SiO_2$  is the commonly used insulating layer for silicon devices, however an additional insulating layer of  $Si_3N_4$  on top of the  $SiO_2$  is sometimes used to reduce the shift of the flatband voltage or threshold voltage<sup>1</sup> caused by ionizing radiation. The effects of the  $Si_3N_4$  will be discussed in section 3.4.

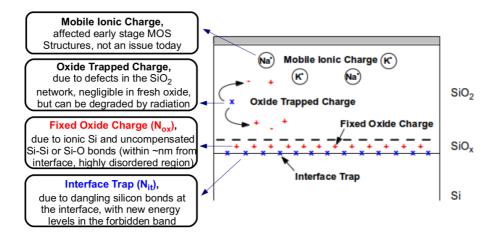

**Figure 3.3**: Schematic illustration of defects in the  $SiO_2$  and at the  $Si-SiO_2$  interface. Picture reproduced from [8].

For a silicon device, there are mainly four kinds of defects in the  $SiO_2$  and at the  $Si-SiO_2$  interface:

Mobile ionic charge For early silicon devices, ions like K<sup>+</sup>, Na<sup>+</sup>, Li<sup>+</sup> and perhaps H<sup>+</sup> existed in the SiO<sub>2</sub>. The ions are positive charged, thus they can move from the Si-SiO<sub>2</sub> interface to the aluminium gate or vice versa. These ions in the SiO<sub>2</sub> are so-called *mobile ionic charges*. The direction that ionic charges move to depends on the electric field inside the oxide. The mobile ionic charges influence the threshold voltage or flatband voltage for early stage silicon devices. However, this is not an issue today.

Oxide trapped charge The electrons and holes produced by ionizing radiation can be captured by electron traps or hole traps in the  $SiO_2$ , and cause *oxide trapped charges*. The oxide trapped charges can be positive or negative, depending on the type of the trap: For an electron trap, the charge stored in the trap is negative when it captures electrons; for a hole trap, the charge is positive when the trap captures holes. The oxide trapped charge is negligible in a fresh oxide, but it can be degraded by radiation damage.

Fixed oxide charge Within several nm from the  $Si-SiO_2$  interface, the region is highly disordered, where the deep level defects are located. The deep levels in the  $SiO_2$  can

<sup>&</sup>lt;sup>1</sup>The shifts of flatband voltage and threshold voltage are usually used to evaluate the densities of oxide charges and interface traps introduced by ionizing radiation. The flatband voltage and threshold voltage will be described in chapter 4.

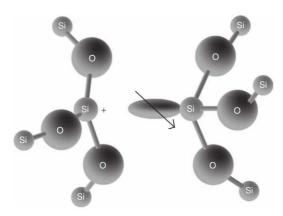

trap holes and form *fixed oxide charges*. The fixed oxide charge is positive and can exist in the silicon device for long time <sup>2</sup>. The fixed oxide charges are also known as E' centres, which consist of two silicon atoms joined by a weak, strained Si-Si bond with an oxygen atom missing, sometimes referred to as oxygen vacancy. Figure 3.4 shows the schematic illustration of an E' center: Each silicon atom is bonded to three oxygen atoms and one silicon atom; the Si-Si bond breaks when a hole is trapped. The density of E' center increases with ionizing radiation dose. It is one of the most important radiation-induced defects.

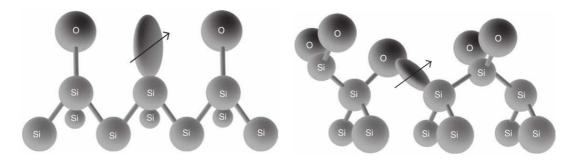

**Figure 3.4**: Schematic illustration of E' center in the SiO<sub>2</sub>. Picture taken from [15].

Interface trap The dangling silicon bonds at the Si-SiO<sub>2</sub> interface are the origin of *interface traps*. The interface traps have energy levels distributed throughout the band gap of silicon. Those energy levels close to the mid-gap contribute to the surface-generation current according to the Shockley-Read-Hall theory. The interface traps are also known as  $P_b$  and  $P_{bo}$  centres. Figure 3.5 shows their configurations.  $P_b$  and  $P_{bo}$  centres exist at the Si-SiO<sub>2</sub> interface of <111> and <100> silicon respectively, however with similar distributions of interface-states levels: One in the upper half of the silicon-band gap, one in the lower half. Compared to <111> silicon, additional centres named  $P_{b1}$  also exist at the Si-SiO<sub>2</sub> interface of the <100> silicon. Their densities can be increased by radiation and decreased through a reaction with hydrogen atoms (known as passivation).

**Border trap** In addition to the fore-mentioned defects, Fleetwood in 1992 suggested that *border traps* should also be included, which have been designated as slow states, near-interface oxide traps, switching oxide traps, and others. The border traps are located within several nm of the Si-SiO<sub>2</sub> interface. They can communicate with electrons and/or holes in the conduction and/or valence band of silicon.

With increasing ionizing radiation dose, the densities of oxide trapped charges, fixed oxide charges, interface traps and border traps increase. In general, the radiation-

<sup>&</sup>lt;sup>2</sup>This can be seen in chapter 11 of the annealing study.

**Figure 3.5**: Schematic illustration of  $P_b$  and  $P_{bo}$  centers. Left:  $P_b$  center at the <111> Si-SiO<sub>2</sub> interface. Right:  $P_{bo}$  center at the <100> Si-SiO<sub>2</sub> interface. Picture taken from [15].

induced defects due to ionizing radiation influence electrical properties and performance of silicon sensors, which can be summarized as follow:

- increase of leakage current dominated by surface current

- increase of full depletion voltage for a p<sup>+</sup>n sensor

- formation of an electron-accumulation layer below the Si-SiO<sub>2</sub> interface

- charge losses close to the Si-SiO<sub>2</sub> interface

- increase of interpixel capacitance for a pixel sensor

- decrease of minority-carrier mobility

- decrease of breakdown voltage

# 3.2. Basic mechanisms of surface damage

The threshold energy for X-rays to cause bulk damage is  $\sim$  300 keV. Therefore, the main damage in silicon sensors at the European XFEL with a typical X-ray energy of 12 keV is surface damage.

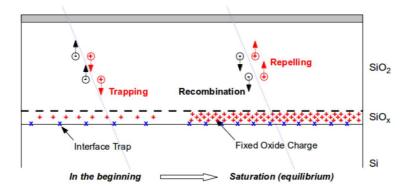

The mechanisms of surface damage, in particular the formation of oxide charges and interface traps, have been described extensively in [16–20]. They can be summarized as follow:

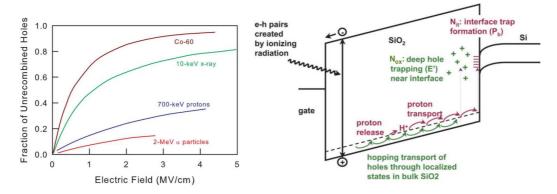

- (1) X-rays (or charged particles) produce electron-hole pairs in the SiO<sub>2</sub>. To produce one electron-hole pair, an average energy of 17 eV is required. Depending on the strength of the electric field in the SiO<sub>2</sub> and the type of incident particles (the density of ionization), a fraction of electrons and holes recombine. Figure 3.6(a) indicates the fraction of unrecombined electrons and holes as function of electric field in the SiO<sub>2</sub> for different radiations: The fraction of electrons and holes escaping from the initial recombination increases with increasing electric field.

- (2) The electrons and holes escaping from the initial recombination either drift to the electrode or to the Si-SiO<sub>2</sub> interface, depending on the direction of the electric field in the SiO<sub>2</sub>. Some of the holes which drift close to the interface, can be captured by oxygen vacancies (most of the vacancies are located in the SiO<sub>2</sub> close to the Si-SiO<sub>2</sub> interface) and form trapped positive charges in the oxide (oxide charges). The

**Figure 3.6**: (a) Fraction of electrons and holes escaping from initial recombination. (b) Mechanisms of formation of oxide charges and interface traps, shown in the band diagrams of SiO<sub>2</sub>, Si-SiO<sub>2</sub> interface and Si. Pictures taken from [20].

reaction is expressed as

$$V_{ox} + h^+ \rightarrow V_{ox}^+ \tag{3.1}$$

where  $V_{ox}$  is denoted as oxygen vacancy,  $h^+$  the hole, and  $V_{ox}^+$  the trapped positive charge. The trapped positive charge,  $V_{ox}^+$ , is able to capture an electron and form a neutral vacancy,

$$V_{ox}^{+} + e^{-} \rightarrow V_{ox} \tag{3.2}$$

(3) During the transport of holes, some react with hydrogenated oxygen vacancies  $(V_{ox}H_2)$  and result in protons  $(H^+)$ . The involved reactions are the capture of holes by  $V_{ox}H_2$  to form  $V_{ox}H_2^+$  and its reverse reaction,

$$V_{ox}H_2 + h^+ \leftrightarrows V_{ox}H_2^+ \tag{3.3}$$

and the release of protons,  $H^+$ , by positively charged oxygenated vacancy,  $V_{ox}H_2^+$ ,

$$V_{ox}H_2^+ \rightarrow V_{ox}H + H^+ \tag{3.4}$$

and the recombination of V<sub>ox</sub>H<sub>2</sub><sup>+</sup> with electrons,

$$V_{ox}H_2^+ + e^- \to V_{ox}H_2$$

(3.5)

(4) Those protons, which drift to the interface, break the hydrogenated silicon bonds (SiH) at the interface and produce dangling silicon bonds (interface traps, denoted as Si·), with energy levels distributed throughout the band gap of silicon. The reaction is written as

$$H^+ + SiH \rightarrow Si \cdot + H_2 \tag{3.6}$$

Figure 3.6(b) shows the mechanisms of formation of oxide charges (with density  $N_{ox}$ ) and interface traps (with density  $N_{it}$ ) in a MOS capacitor biased with positive

gate voltage. The values of  $N_{ox}$  and  $N_{it}$  induced by X-ray ionizing radiation mainly depend on dose, electric field in the SiO<sub>2</sub>, annealing time and temperature, crystal orientation, and quality of the oxide, which will be discussed in section 3.4 in detail.

## 3.3. Modelling of damage mechanisms

The change of the densities of oxide charges and interface traps with irradiation can be modelled with a set of equations related to drift and diffusion of free carriers in the SiO<sub>2</sub>, trapping of electrons and holes by neutral defects, and reactions of passivated silicon bonds at the Si-SiO<sub>2</sub> interface with protons.

**Generation of electron-hole pairs** To produce an electron-hole pair in SiO<sub>2</sub>,  $17\pm1$  eV is needed for X-rays and other kinds of ionizing radiations. According to this energy, the electron-hole pairs per unit volume per rad is:  $g_0 = 8.1 \times 10^{14}$  pairs/(cm<sup>3</sup>·Gy). But this density is quickly reduced by the initial recombination of electrons and holes.

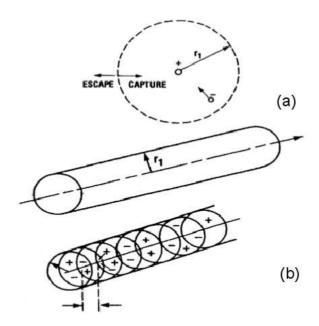

**Initial recombination process** When electrons and holes are produced by radiations, they will recombine instantly. The fraction of electrons and holes escaping from the initial recombination mainly depends on two factors: the strength of the electric field in the SiO<sub>2</sub> during irradiation which separates the electrons and holes, and the line density of electron-hole pairs. The line density is determined by the linear energy transfer (LET), which depends on the type of incident particle and its energy (as already seen in figure 3.6(a)). For a higher line density of electron-hole pairs, the average separation distance between electron-hole pairs is small; therefore, more recombination between electrons and holes occur. There are two models describing the initial recombination: geminate recombination model and columnar recombination model, which can be seen in figure 3.7(a) and (b). In the geminate recombination model, the average separation distance between electron-hole pairs is much larger than the thermalization distance, which is the distance between the electron and the hole in a pair. The charges in one electron-hole pair can be treated as an "isolated pair", which have a mutual Coulomb attraction. The electron and the hole in the "isolated pair" drift in opposite directions under the driving force of the electric field in the SiO<sub>2</sub> and have a random diffusion motion due to the thermal velocity. But interactions between one "isolated pair" and another are neglected. In the columnar recombination model, the separation distance between the electron-hole pairs is much smaller than the distance between the electron and the hole in one electron-hole pair. There are more electrons "staying" closer to the hole than the electron in the electron-hole pair; therefore, the recombination probability between electrons and holes is much greater than in the case described by geminate model [19]. Hence, it is expected that the geminate recombination model describes the case for low dose rates better, however the columnar recombination model for high dose rates.

For the geminate recombination model, the generation probability of electron-hole pairs, Y(E), escaping from the initial recombination can be described as function of the electric field E in the SiO<sub>2</sub>:

**Figure 3.7**: Schematic diagrams of the models for initial recombination: (a) geminate model and (b) columnar model.

$$Y(E) = Y_0 + (1 - Y_0) \left(\frac{E}{E + E_0}\right)^m \tag{3.7}$$

with  $Y_0 = 0.065$ , m = 0.9,  $E_0 = 1.35$  MV/cm for 10 keV X-rays and m = 0.7,  $E_0 = 0.55$  MV/cm for gamma-rays ( $^{60}$ Co).  $Y_0$  is the fraction of electrons and holes escaping from the initial recombination at zero field due to the thermal agitation [21].

Hence, the generation rate of electrons and holes, G(E), can be written as

$$G(E) = g_0 \cdot Y(E) \cdot D' \tag{3.8}$$

where D' is the dose rate of the irradiation.

**Transport of electrons**, holes and protons The reactions of (3.1)-(3.6) can be formulated into continuity equations describing the transport of electrons, holes and protons. For each kind of charge carrier, the continuity equation is given by

$$\frac{\mathrm{d}n_i}{\mathrm{d}t} + \frac{1}{q_0} \nabla \cdot \vec{\mathbf{J}}_i = G_i - R_i \tag{3.9}$$

where  $n_i = n_i(\vec{\mathbf{r}}, t)$  is the density for each kind of charge carrier (labelled as i) which is a function of position  $\vec{\mathbf{r}}$  and time t.  $\vec{\mathbf{J}}_i$ ,  $G_i$  and  $R_i$  are the current density, generation rate and reaction rate (or call it consuming rate) of each kind of charge carrier. To be more specific, the density of electrons is denoted as n, holes as p and protons as  $n_{H^+}$ . Considering a simple 1D structure for SiO<sub>2</sub>, the space and time dependent continuity equations are

$$\frac{\partial n}{\partial t} = -\frac{1}{q_0} \frac{\partial |\vec{\mathbf{J}}_n|}{\partial x} + G_n - R_n \tag{3.10}$$

$$\frac{\partial p}{\partial t} = -\frac{1}{q_0} \frac{\partial |\vec{\mathbf{J}}_p|}{\partial x} + G_p - R_p \tag{3.11}$$

$$\frac{\partial n_{H^{+}}}{\partial t} = -\frac{1}{q_{0}} \frac{\partial |\vec{\mathbf{J}}_{n_{H^{+}}}|}{\partial x} + G_{n_{H^{+}}} - R_{n_{H^{+}}}$$

(3.12)

where  $G_n$ ,  $G_p$  and  $G_{n_{H^+}}$  are the generation rates, and  $R_n$ ,  $R_p$  and  $R_{n_{H^+}}$  are the reaction rates of electrons, holes and protons.  $\vec{J}_n$ ,  $\vec{J}_p$  and  $\vec{J}_{n_{H^+}}$  are the current densities of electrons, holes and protons, respectively. They can be expressed as

$$\vec{\mathbf{J}}_n = q_0 n \mu_n \vec{\mathbf{E}} + q_0 D_n \frac{\partial n}{\partial x}$$

(3.13)

$$\vec{\mathbf{J}}_{p} = q_{0}p\mu_{p}\vec{\mathbf{E}} - q_{0}D_{p}\frac{\partial p}{\partial x}$$

(3.14)

$$\vec{\mathbf{J}}_{n_{H^{+}}} = q_{0}n_{H^{+}}\mu_{H^{+}}\vec{\mathbf{E}} + q_{0}D_{H^{+}}\frac{\partial n_{H^{+}}}{\partial x}$$

(3.15)

with  $\mu_n$ ,  $\mu_p$  and  $\mu_{H^+}$  the mobilities of electrons, holes and protons in the SiO<sub>2</sub>.  $D_n$ ,  $D_p$  and  $D_{H^+}$  are the electron, hole and proton diffusivities in the SiO<sub>2</sub>.  $\vec{\bf E}$  is an electric field vector, which is a function of position:  $\vec{\bf E} = \vec{\bf E}(x)$  for 1D case.  $\vec{\bf E}(x)$  can be obtained by solving Poisson's equation,

$$\frac{\partial E}{\partial x} = \frac{q_0}{\varepsilon_{SiO_2}} \left( -n + p + n_{H^+} + n_{V_{ox}^+} + n_{V_{ox}H_2^+} \pm n_{Si.} \right)$$

(3.16)

where  $n_{V_{ox}^+}$  is the concentration of positively charged oxygen vacancies,  $n_{V_{ox}H_2^+}$  the concentration of hydrogenated oxygen vacancies after trapping holes, and  $n_{Si}$ . the concentration of charged dangling silicon bonds at the Si-SiO<sub>2</sub> interface region. However, the sign of  $n_{Si}$  depends on the type of the interface trap (acceptor or donor) and the trap filling.

**Formation of trapped charges and interface traps** During the transport of electrons, holes and protons, they can be involved in the reactions (3.1)-(3.6) and result in the formation of oxide-trapped charges and interface traps. The equations for the reactions are given by

$$\frac{\partial n_{V_{ox}^+}}{\partial t} = \frac{1}{q_0} \left( \sigma_{V_{ox}tp} |\vec{\mathbf{J}}_p| N_{V_{ox}} - \sigma_{V_{ox}^+rn} |\vec{\mathbf{J}}_n| n_{V_{ox}^+} \right)$$

(3.17)

$$\frac{\partial n_{V_{ox}H_{2}^{+}}}{\partial t} = \frac{1}{q_{0}} \left( \sigma_{V_{ox}H_{2}tp} |\vec{\mathbf{J}}_{p}| N_{V_{ox}H_{2}} - \sigma_{V_{ox}H_{2}^{+}rn} |\vec{\mathbf{J}}_{n}| n_{V_{ox}H_{2}^{+}} \right) - \left( r_{V_{ox}H_{2}^{+}rp} + r_{V_{ox}H_{2}^{+}rH^{+}} \right) n_{V_{ox}H_{2}^{+}}$$

(3.18)

$$\frac{\partial n_{Si.}}{\partial t} = \frac{1}{q_0} \sigma_{it} |\vec{\mathbf{J}}_{H^+}| N_{SiH}$$

(3.19)

The description of the symbols in the above equations (3.17)-(3.19) are listed in table 3.1.

| Symbol                      | Description                                         |

|-----------------------------|-----------------------------------------------------|

| $\overline{N_{V_{ox}}}$     | concentration of $V_{ox}$                           |

| $N_{V_{ox}H_2}$             | concentration of $V_{ox}H_2$                        |

| $N_{SiH}$                   | concentration of SiH                                |

| $\sigma_{V_{ox}tp}$         | capture cross section of holes by $V_{ox}$          |

| $\sigma_{V_{ox}^+rn}$       | capture cross section of electrons by $V_{ox}^+$    |

| $\sigma_{V_{ox}H_2tp}$      | capture cross section of holes by $V_{ox}H_2$       |

| $\sigma_{V_{ox}H_2^+rn}$    | capture cross section of electrons by $V_{ox}H_2^+$ |

| $r_{V_{ox}H_2^+rp}$         | reaction rate of $V_{ox}H_2^+$ dissolved to holes   |

| $r_{V_{ox}H_{2}^{+}rH^{+}}$ | reaction rate of $V_{ox}H_2^+$ dissolved to protons |

| $\sigma_{it}$               | cross section of protons react with SiH             |

**Table 3.1**: Description of symbols in the equations (3.17)-(3.19)

Hence, the generation rates and reaction rates in the continuity equations (3.10)-(3.12) can be expressed as

$$G_n - R_n = G - \frac{1}{q_0} \sigma_{V_{ox}^+ rn} |\vec{\mathbf{J}}_n| n_{V_{ox}^+} - \frac{1}{q_0} \sigma_{V_{ox} H_2^+ rn} |\vec{\mathbf{J}}_n| n_{V_{ox} H_2^+}$$

(3.20)

$$G_p - R_p = G + r_{V_{ox}H_2^+ rp} n_{V_{ox}H_2^+} - \frac{1}{q_0} \sigma_{V_{ox}tp} |\vec{\mathbf{J}}_p| N_{V_{ox}} - \frac{1}{q_0} \sigma_{V_{ox}H_2tp} |\vec{\mathbf{J}}_p| N_{V_{ox}H_2}$$

(3.21)

$$G_{H^{+}} - R_{H^{+}} = r_{V_{ox}H_{2}^{+}rH^{+}} n_{V_{ox}H_{2}^{+}} - \frac{1}{q_{0}} \sigma_{it} |\vec{\mathbf{J}}_{H^{+}}| N_{SiH}$$

(3.22)

Solving the above electron- and hole-continuity equations, the Poisson equation for the electric field, and the equations related to those reactions, the concentrations of trapped charges by oxygen vacancies ( $n_{V_{ox}^+}$ ) and dangling silicon bonds are obtained. Thereafter, the oxide-charge density,  $N_{ox}$ , defined as the density of equivalent charges at the Si-SiO<sub>2</sub> interface can be determined by integrating the concentration of trapped charges by oxygen vacancies,  $n_{V_{ox}^+}$ , throughout the entire SiO<sub>2</sub> region. These partial differential equations (PDEs) are highly coupled; hence, one needs to turn to a numerical scheme with dedicated algorithms and a finite element method (FEM) in order to solve the equations.

# 3.4. Factors influencing the densities of oxide charges and interface traps

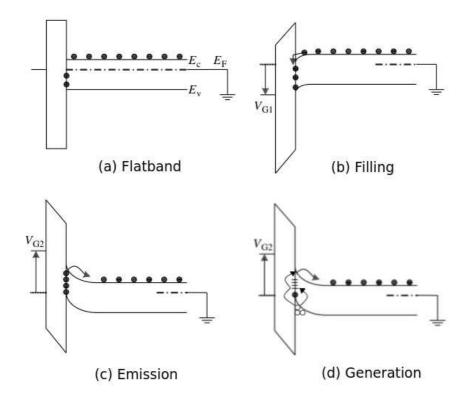

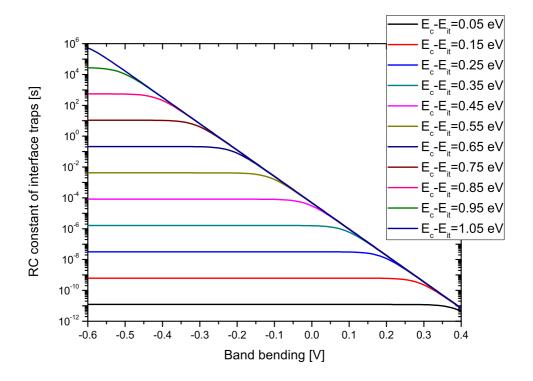

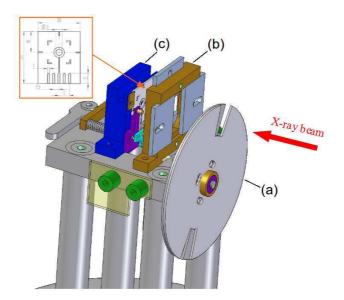

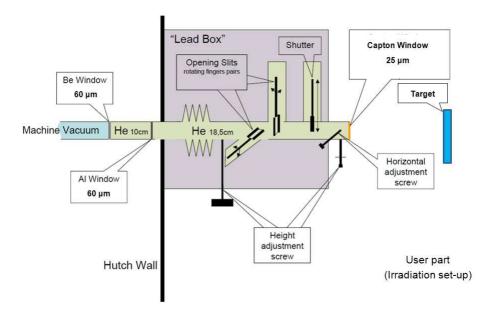

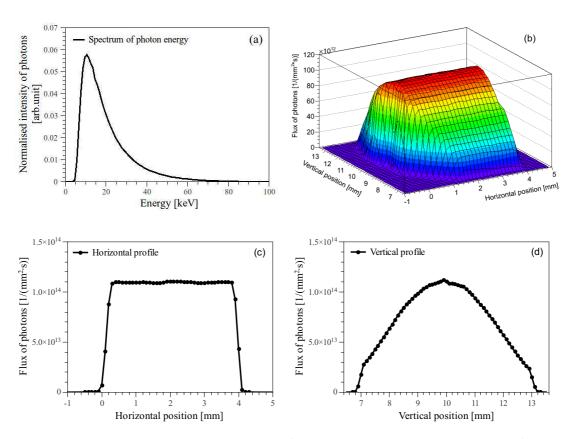

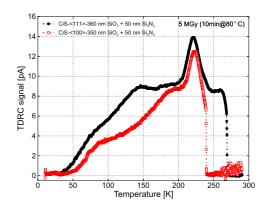

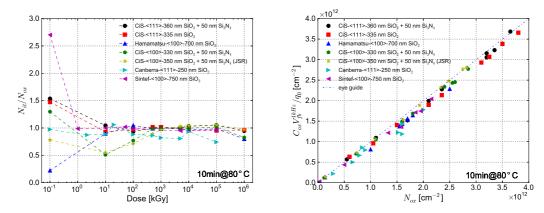

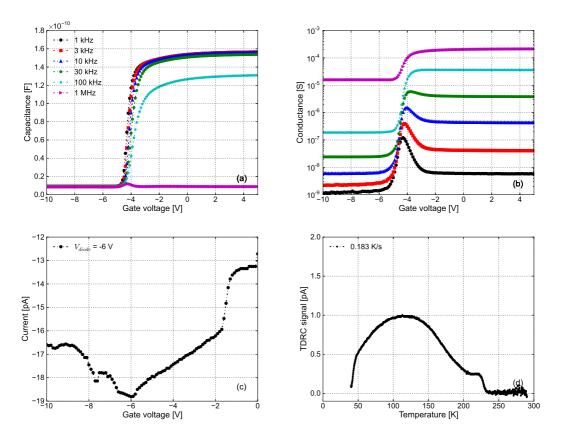

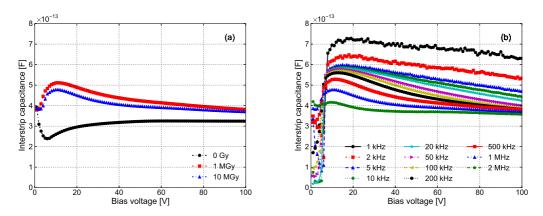

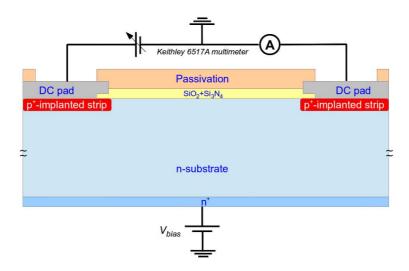

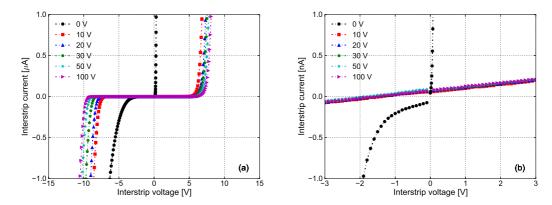

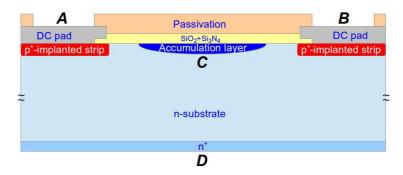

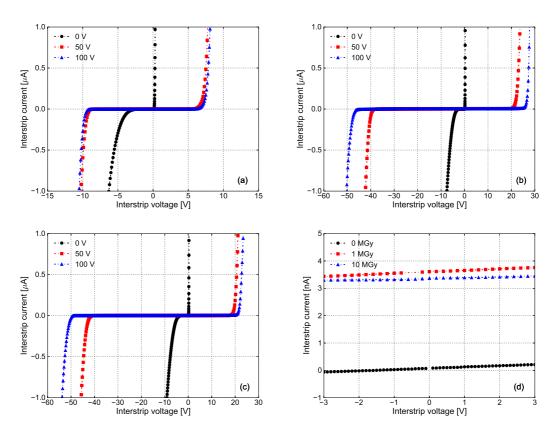

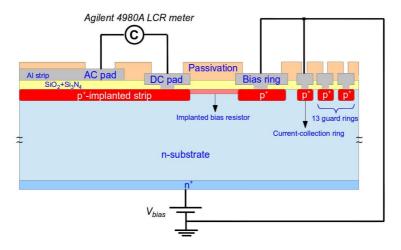

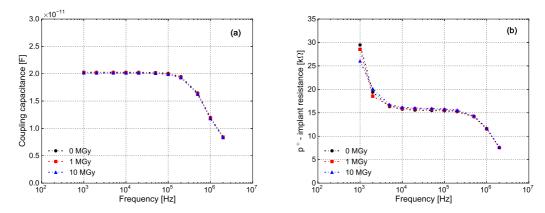

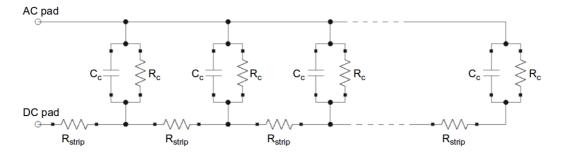

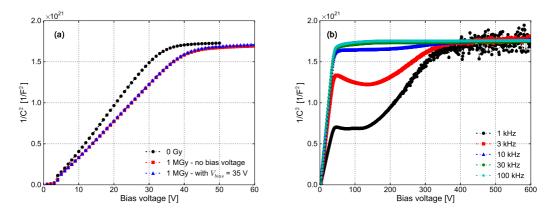

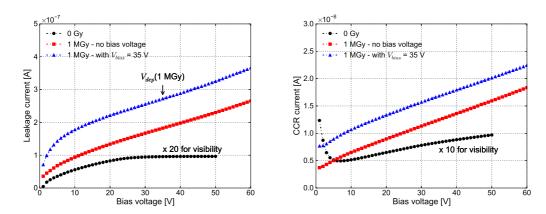

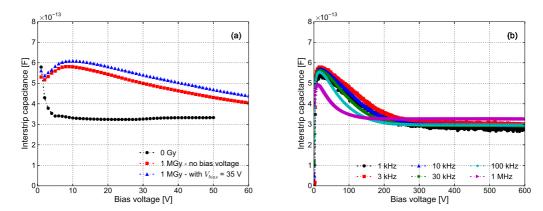

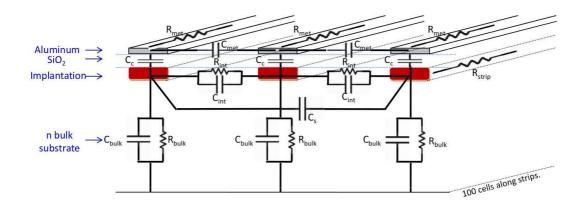

The oxide-charge density,  $N_{ox}$ , and interface-trap density,  $N_{it}$ , are very sensitive to ionizing radiation and the operating conditions: For example, the total ionizing dose (TID), dose rate and bias voltage of silicon devices which leads to different electric fields in the SiO<sub>2</sub>. In addition, the oxide thickness, additional insulating layer on top of the SiO<sub>2</sub>, post-irradiation conditions also influence  $N_{ox}$  and  $N_{it}$ . These factors will be discussed separately.