# 2001 - 2004 R&D on CMOS sensors for Charged Particle Tracking at a Future Linear Collider Vertex Detector

07.05.2003

M. Winter on behalf of the collaboration of

DAPNIA - DESY - Dubna - Univ.Geneva - IReS&LEPSI - Univ.Hamburg - NIKHEF/Amsterdam

- Reminder: principle of operation of CMOS sensors

- Summary of sensor prototypes fabricated since 1999

- New results on tracking performances of small sensors

- Test results of first real scale prototype

- Test results of low doping substrate sensor

- Radiation tolerance

- Next major R&D steps: Sensor & System Developments

- Summary

## **Advantages of Monolithic Active Pixel Sensors:**

# \* MAPS combine advantages of CCDs and of Hybrid Pixels:

- they provide as good spatial resolution as CCDs & can be thinned down to the same level

- they are much more resistent to neutron radiation and are potentialy much faster than CCDs

# **Principle of Operation:**

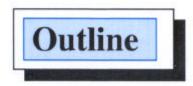

- \* p-type low-resistivity Si

- $\diamond$  signal generated in epitaxial layer (low doping)  $\rightarrow$   $\mathbf{Q}_{mip} \sim$  80 e<sup>-</sup>-h pairs /  $\mu m$

- signal charge collected by n-well

- excess carriers diffuse thermally to nwells with help of reflection on boundaries with p-well and substrate (high doping)

- ⋄ no external depletion voltage

- ⇒ watch feature size, epitaxial layer thickness, nb of metal layers, yield, ...

Figure 1: Schematic view of the charge collection in a CMOS sensor pixel designed for charged particle tracking.

# **Summary of prototypes fabricated**

▶ 6 prototypes fabricated since 1999 (5 tested with 120 GeV/c  $\pi^-$  CERN-SPS)

| sensor generation | year | process                                                | epitax.       | pitch        | metal | peculiarity                                                             |

|-------------------|------|--------------------------------------------------------|---------------|--------------|-------|-------------------------------------------------------------------------|

| MIMOSA-1          | 1999 | $egin{array}{c} \mathbf{AMS} \\ 0.6 \mu m \end{array}$ | $14\mu m$     | <b>20</b> μm | 3M    | thick<br>epitaxy                                                        |

| MIMOSA-2          | 2000 | MIETEC $0.35 \mu m$                                    | <b>4.2</b> μm | <b>20</b> μm | 5M    | thin<br>epitaxy                                                         |

| MIMOSA-3          | 2001 | <b>IBM 0.25</b> μm                                     | $2\mu m$      | <b>8</b> µm  | 3M    | $\begin{array}{c} \textbf{deep} \\ \textbf{sub-}\mu\dot{m} \end{array}$ |

| MIMOSA-4          | 2001 | $0.35 \mu m$                                           | 0!            | <b>20</b> μm | 3M    | low doping<br>substrate                                                 |

| MIMOSA-5          | 2001 | $egin{array}{c} \mathbf{AMS} \\ 0.6 \mu m \end{array}$ | $14\mu m$     | <b>17</b> μm | 3M    | real scale<br>(10 <sup>6</sup> pixels)                                  |

| MIMOSA-6          | 2002 | <b>ΜΙΕΤΕ</b> C <b>0.35</b> μm                          | <b>4.2</b> μm | <b>28</b> μm | 5M    | column // r.o.<br>integ. sparsif.                                       |

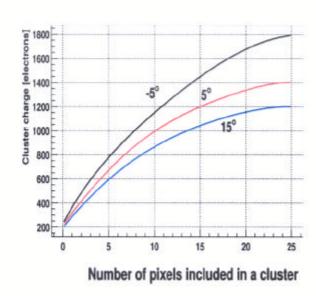

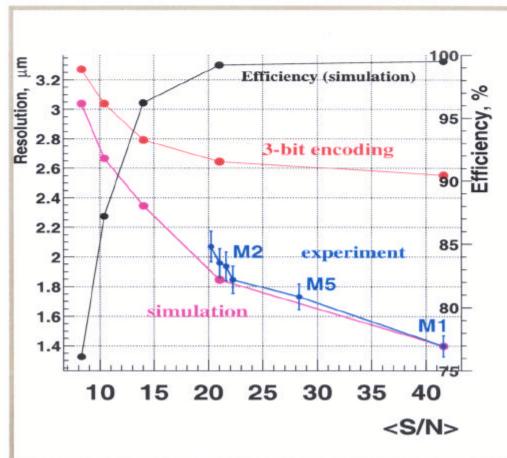

# **Spatial resolution**

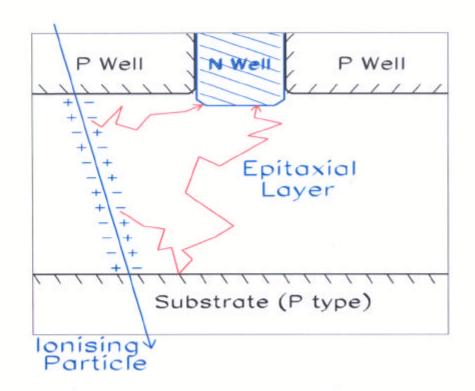

$ightharpoonup \sigma_{sp} \sim$  1.5 (2.2)  $\mu m$  with 14 (4)  $\mu m$  epitaxial layer

**▶** single point resolution as a function of ADC-bit encoding:

$\sigma_{sp}\sim$  2-2.5  $\mu m$  for 3 bits ( $\sim$  3-4  $\mu m$  for 1 bit ... )

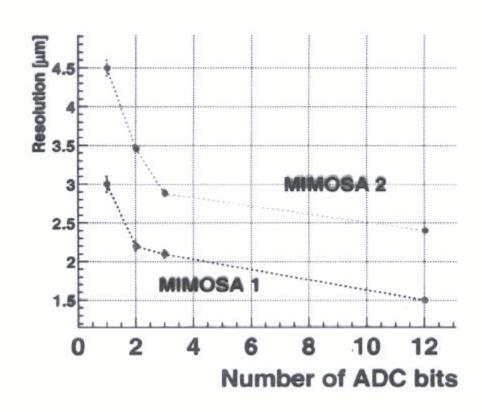

▶ double track resolution: excellent down to 30 µm distance

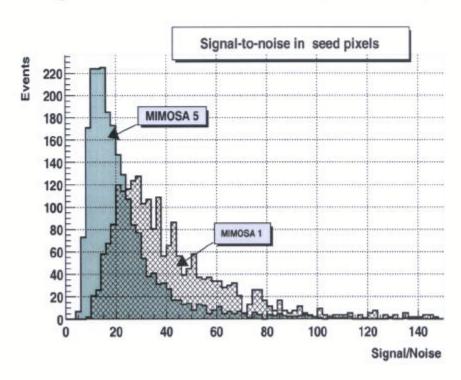

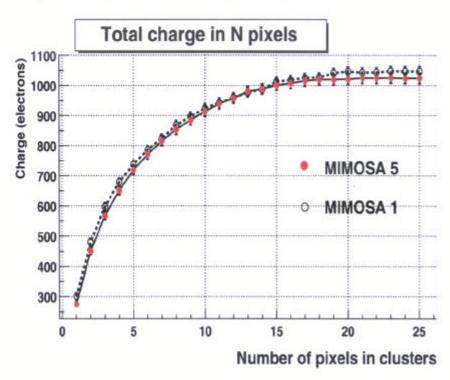

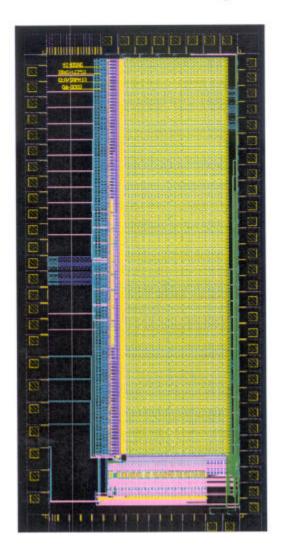

## MIMOSA-5: 1st real scale prototype

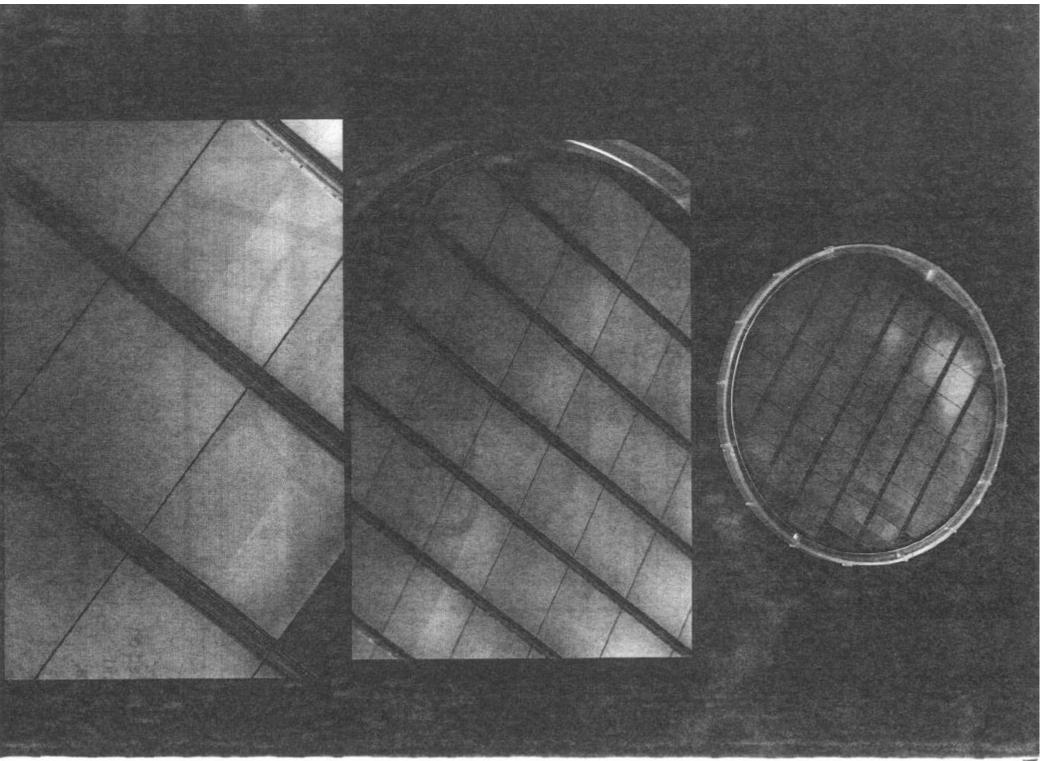

- ▶ chip of 4 matrices of 512x512 (17x17  $\mu m^2$ ) pixels read-out in parallel, etched to 120  $\mu m$   $\hookrightarrow$  exposed to 120 GeV/c  $\pi^-$  beam at CERN-SPS

- comparison with MIMOSA-1 (same 0.6  $\mu m$  AMS process, but 64x64 pixels)

▶ prelim. result: detection efficiency  $\sim 99.3 \%$ ,  $\sigma_{sp} \sim 1.7 \ \mu m$ ,  $\sigma_{\overline{gain}} \sim 0.2 \%$  (twice noise of M1 due to different <u>serial</u> r.o. architecture)

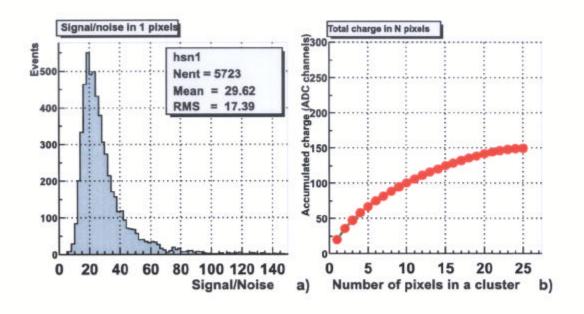

## Test results with MIMOSA-4 (1/2)

$\triangleright$  0.35  $\mu m$  AMS process without epitaxial layer but with low doping (resistivity) substrate

- ▶ Observed performances with 120 GeV/c  $\pi^-$  at CERN-SPS ( $T_{Room}$ ):

- $\clubsuit$  detection efficiency  $\sim 99.7 \%$   $\clubsuit$  single point resolution  $\sim 4 \ \mu m \ (20 \ \mu m \ pitch)$

- ► Low temperature still improve sensor performances (studies under way)

- ⇒ Technology without epitaxial layer seems worth investigating & optimising

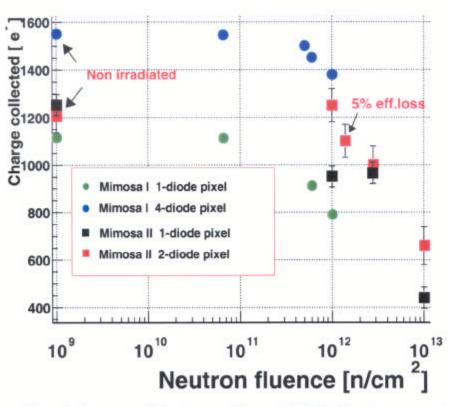

#### **Radiation tolerance**

► Neutron irradiations up to  $10^{13} n_{eq}/cm^2$

$\hookrightarrow$  fluences of  $\lesssim 10^{12} n_{eq}/cm^2$  are still acceptable (T effect ?)

- ▶ Ionising radiation: few 100 kRad acceptable (better if T << 0 $^{\circ}$ C?)

- $\hookrightarrow$  exact source(s) of performance loss under investigation

- ▶ Ccl: radiation tolerance at a FLC should not be an issue (yearly:  $\sim 10^9 n_{eq}/cm^2$  and 50 kRad) X Safety Factor of 10 & 5?

#### Plans for 2003 - 2004

- ► Sensor development towards fast signal processing & data compression:

- ullet MIMOSA-6: col. // r.o. & integ. signal proc. o tests at CERN-SPS in June

- MIMOSA-7: alternative signal collection & processing architecture (photoFET)

- $\hookrightarrow$  design in 0.25  $\mu m$  AMS (8  $\mu m$  epitaxy)  $\to$  submission in June  $\to$  tests in Autumn

- MIMOSA-8/9: best out of MIMOSA-6/7 → fast medium size sensor < Summer 2004</li>

- ► System integration studies have started:

- ⋄ DAS card being designed

- $\diamond$  detailed effect of detector material, pixel size, etc. on  $\gtrsim$  500 GeV physics

- ♦ GEANT-4 description of CMOS Vertex Detector started

- ⋄ pulsed powering studies with MIMOSA-5 in preparation

- $\diamond$  estimation of limit in  $\overline{P_{diss}}$  compatible with modest active cooling

- $\diamond$  achieve  $\lesssim$  50  $\mu m$  thinning on real scale chip (MIMOSA-5)

- ⇒ preliminary ladder prototype in 2005 (?)

- ► Find optimum of granularity\*signal proc. speed\*mat. budget with physics simulations

# Signal processing

► Governed by  $N(e_{BS}^{\pm})$  in 1st Vertex Detector layer:

$$N_{\pm}^{sim}(90^{\circ}) \gtrsim 5~e^{\pm}$$

/ cm<sup>2</sup> / BX at 500 GeV (R=15 mm)

$\hookrightarrow$  occupancy  $\gtrsim$  3-5 % in 100  $\mu s$  (m<sub>clust</sub>  $\sim$  5)

- ► Safety factors (simulation accuracy, uncertainty on B, higher  $\sqrt{s}$ , shorter  $\Delta t_{BX}$ )  $\rightsquigarrow$  occ.  $\gtrsim$  15-25 % in 100  $\mu s$

- ► Goal:  $\mathbf{t}_{L1}\sim$  25-50  $\mu s$  (R&D needed)  $\mathbf{t}_{lect}^{L2-5}\sim$  100  $\longrightarrow$  200  $\mu s$  (no major difficulty)

- ► major obstacle: data flux (L1)

- $\hookrightarrow$  15 bits/pixel,  $\mathbf{t}_{L1}\sim$  25  $\mu s\longrightarrow\sim$  500 Gbits/s/10<sup>6</sup> pixels ( $\mathbf{e}_{BS}^{\pm}$ : 5 Gbits/s)

- ⇒ Next CMOS sensor prototypes address Signal Processing Speed AND Data Compression

## MIMOSA-6: 1st sensor with col.// r.o. & integ.sparsif.

▶ 1st sensor with sparsification integrated / substrate & column // r.o.:

- > amplification (x5.5) and noise suppression (CDS) on pixel

- > discriminator integrated on chip periphery (1 per column)

- $\clubsuit$  0.35  $\mu m$  MIETEC technology (same as MIMOSA-2)

- ♣ 30 columns read-out in ↓↓ (128 pixels per column)

- ⇒ 30 MHz r.o. frequency but 6 clock cycles per pixel

⇒ 5 MHz effective r.o. frequency

- $\clubsuit$  pixels of 28  $\mu m$  pitch (29 transistors, 3 capacitors)

- <  $P_{diss} \sim$  500  $\mu W$  per column and frame r.o. cycle

A tests under way in Strasbourg and Saclay

## Fast Data Processing: Effect of Increased Noise

- $\blacktriangleright$  on-chip data proc. to reduce data flux ( $\emptyset$ ) due to fast r.o. of very granular sensors

- → pre-amplif., noise supp., ADC, discri., ... shared between pixel and chip periphery

- $\Rightarrow$  noise may increase substantially  $\rightarrow$  csq on  $\epsilon_{det}$  &  $\sigma_{sp}$  ?

- ► Study based on M-1,-2,-5 data:

- $\epsilon_{det} \gtrsim$  96 % if S/N  $\gtrsim$  14

- ullet  $\sigma_{sp}\lesssim$  3  $\mu m$  even if S/N  $\sim$  10 and only 3-bit encoding

# View of the VXD in MOKKA

- 50 μm thick carbon fibre mecanical support

- → 50 μm thick CMOS sensor

$$*X/X_0 \approx 0.08 \%$$

- tracking algorithm implementation

- impact parameter resolution

• Caution! This is just a starting point, the final geometry may be totally different.

# **Distribution of Tasks**

| R&D<br>Topic     | Univ.<br>Geneva | Univ.<br>Hamburg | IReS-<br>LEPSI | DESY         | NIKHEF<br>Amster. | DAPNIA       |

|------------------|-----------------|------------------|----------------|--------------|-------------------|--------------|

| Intrinsic Perfo. |                 |                  | X              |              | X                 | X            |

| R.O.Circuits     |                 |                  | X              |              |                   | X            |

| Chip Tests       |                 | $\mathbf{X}$     | $\mathbf{X}$   | $\mathbf{X}$ |                   | $\mathbf{X}$ |

| Rad. Tolerance   |                 | X                | X              | X            | X                 |              |

| DAS circuits     | X               |                  |                |              |                   |              |

| Thinning         |                 |                  | X              | X            | X                 |              |

| Mech. & Cool.    |                 | X                |                | X            | X                 |              |

# **Summary**

- ⋄ Several requirements for this application are already fulfiled: detection efficiency, spatial resolution (3-bits), double hit resolution, radiation tolerance (~), real scale sensors, low doping substrate technology, etc.

- $\diamond$  Until 2004, substantial progress expected on fast signal processing (goal  $\sim$  25  $\mu s$ ) and system integration  $\rightarrow$  prototype ladder in 2005 (?)