# S2E Simulations on Jitter Issues for the European XFEL Project

- Layout (10AUG04 Version) with Two BC Stages -

Yujong Kim, K. Flöttmann, and T. Limberg DESY Hamburg, Germany

**Dongchul Son**

The Center for High Energy Physics, Korea

Yujong.Kim@DESY.de, http://www.desy.de/~yjkim

TESLA-S2E-46

#### **Contents**

- Short Introduction to Two Linac Layouts for European XFEL Project

- Current Linac Layout (13JAN04 Version) with a Double Chicane

- Alternative Linac Layout (10AUG04 Version) with Two BC stages

- **S2E Simulations to Compare Two Layouts Under Same Jitter Tolerances**

- **☐** FEL Performance Based New Threshold of Jitter Sensitivity

- FEL Performance Based Jitter Tolerance Set for Alternative Layout

- **□** 423 Times S2E Simulation with Alternative Linac Layout

- **Summary**

- **Acknowledgments**

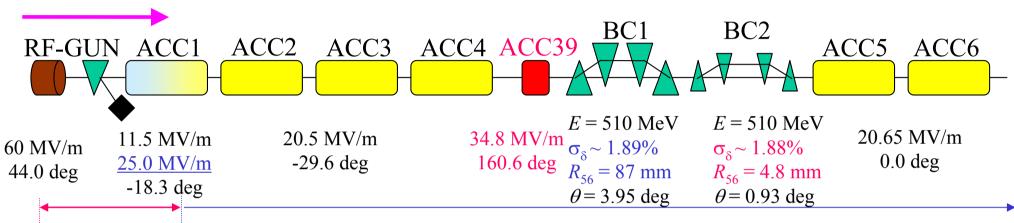

# **Current Layout for XFEL (13JAN04)**

#### With Old European XFEL Injector, ε<sub>n</sub>= 0.90 μm

Q=1.0 nC $\sigma_z = 1.76 \text{ mm} \longrightarrow 113 \text{ } \mu\text{m} \longrightarrow 20.5 \text{ } \mu\text{m}$ e-beam

**ASTRA** with **Space Charge** 12.0444 m  $0.0\,\mathrm{m}$

To the end of Linac: ELEGANT with CSR

with geometric wakefields without space charge

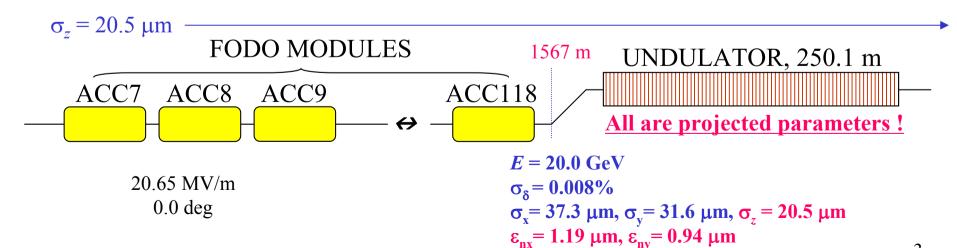

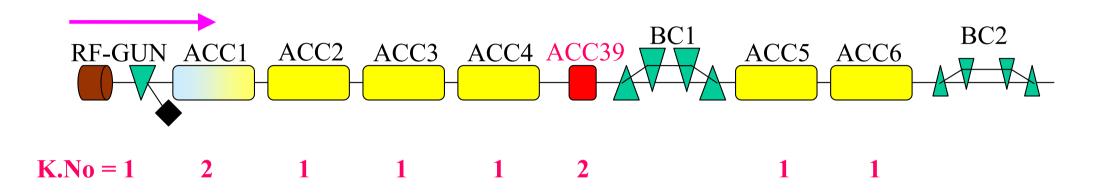

# Klystron Distribution of Current Layout

Here K.No means the number of Klystron per module!

Multi-Klystron before BC2 reduces the jitter sensitivity in ACC234 and ACC39 modules

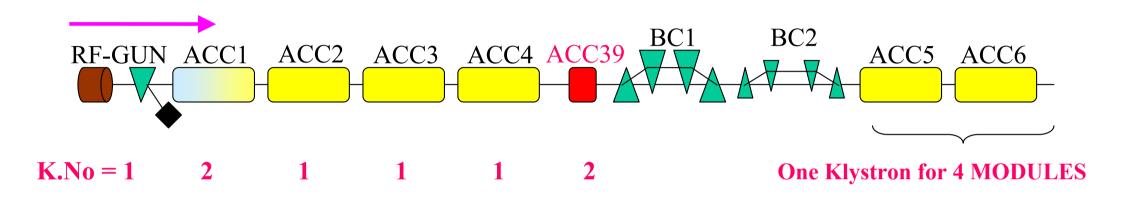

# **Alternative Layout for XFEL (10AUG04)**

#### With New European XFEL Injector, ε<sub>n</sub>= 0.88 μm

Q = 1.0 nC $\sigma_z = 1.72 \text{ mm} \longrightarrow 94 \mu\text{m}$ → 21.6 µm

BC2 ACC3 ACC4 ACC39 ACC6 ACC2 ACC5 RF-GUN ACC1

12.8 MV/m 60 MV/m 24.84 MV/m 40.0 deg -25.0 deg

e-beam

20.2 MV/m -25.0 deg

E = 518 MeV34.5 MV/m  $\sigma_{\delta}$   $\sim 1.87\%$ 165.9 deg  $R_{56} = 87 \text{ mm}$  $\theta$  = 3.95 deg

0-20.5-35 MV/m -44.5 deg

E = 518-760-1100 MeV $\sigma_{\delta} \sim 1.87 \text{--} 1.33 \text{--} 0.9\%$  $R_{56} \sim 5.3 \text{ mm}$  $\theta \sim 0.93 \deg$

**ASTRA** with **Space Charge** 12.9869 m  $0.0\,\mathrm{m}$

To the end of Linac: ELEGANT with CSR

with geometric wakefields without space charge

$\sigma_z = 21.6 \, \mu m$ **FODO MODULES**

1579 m ACC7 ACC8 ACC120 ACC9  $\leftrightarrow$

UNDULATOR, 250.1 m

All are projected parameters!

20.38 MV/m 0.0 deg

$E = 20.0 \, \text{GeV}$  $\sigma_{s} = 0.0088\%$  $\sigma_x = 34.2 \ \mu \text{m}, \ \sigma_v = 29.5 \ \mu \text{m}, \ \sigma_z = 21.6 \ \mu \text{m}$  $\varepsilon_{\rm nx}$ = 1.044  $\mu$ m,  $\varepsilon_{\rm nv}$ = 0.896  $\mu$ m

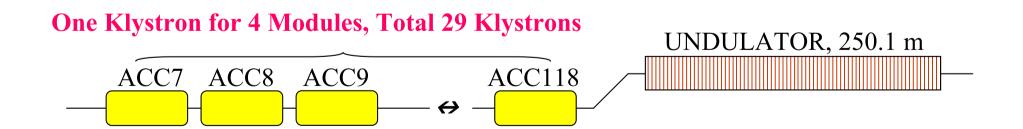

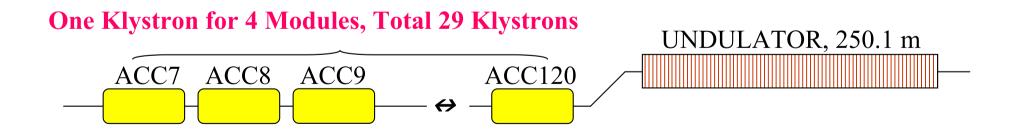

# Klystron Distribution of Alternative Layout

Here K.No means the number of Klystron per module!

Multi-Klystron before BC2 reduces the jitter sensitivity in ACC334, ACC39, and ACC56

# Papers On Two Linac Layouts for XFEL

#### On Current Linac Layout (13JAN04 Version) with a Double Chicane

**S2E** simulation on Linac Optimization:

**APAC2004, EPAC2004**

by Yujong Kim, K. Flöttmann, T. Limberg, M. Dohlus, and D. Son

**S2E Simulations on Jitter:**

**EPAC2004**

by Yujong Kim, K. Flöttmann, and T. Limberg, and D. Son

#### On Alternative Linac Layout (10AUG04 Version) with Two BC Stages

**S2E** simulation on Linac Optimization:

LINAC2004

by Yujong Kim, K. Flöttmann, T. Limberg, and D. Son

**S2E Simulations on Jitter:**

Not yet reported due to limited available computer, maybe, at PAC2005

# Sensitivity & Tolerance Set for Current Layout

#### Linac Performance Based Tolerance (refer to our EPAC2004 paper)

#### For each Klystron

| or cacif ixiy ser on  | Sensitivity      | TOL-I (rms)     | TOL-II (rms)  0.3 ps |  |

|-----------------------|------------------|-----------------|----------------------|--|

| dT                    | 0.50 ps          | 0.1 ps          |                      |  |

| dQ                    | - 6.10%          | 1.0%            | 1.5%                 |  |

| ACC1C1234 Phase       | <b>0.20 deg</b>  | <b>0.05 deg</b> | <b>0.07 deg</b>      |  |

| ACC1C1234 dV/V        | <b>- 0.17%</b>   | 0.02%           | 0.03%                |  |

| ACC1C5678 Phase       | <b>0.10 deg</b>  | <b>0.05 deg</b> | <b>0.07 deg</b>      |  |

| <b>ACC1C5678 dV/V</b> | -0.08%           | 0.02%           | 0.03%                |  |

| ACC234 Phase          | -0.056 deg       | <b>0.05 deg</b> | <b>0.07 deg</b>      |  |

| ACC234 dV/V           | <b>-0.06%</b>    | 0.02%           | 0.03%                |  |

| ACC39 Phase           | <b>-0.08 deg</b> | <b>0.05 deg</b> | <b>0.07 deg</b>      |  |

| ACC39 dV/V            | 0.19%            | 0.02%           | 0.03%                |  |

| BC1 dI/I              | 0.02%            | 0.02%           | 0.02%                |  |

| BC2 dI/I              | 0.31%            | 0.02%           | 0.02%                |  |

| ACC5678 Phase         | 4.19 deg         | <b>0.05 deg</b> | <b>0.07 deg</b>      |  |

| ACC5678 dV/V          | 0.028%           | 0.02%           | 0.03%                |  |

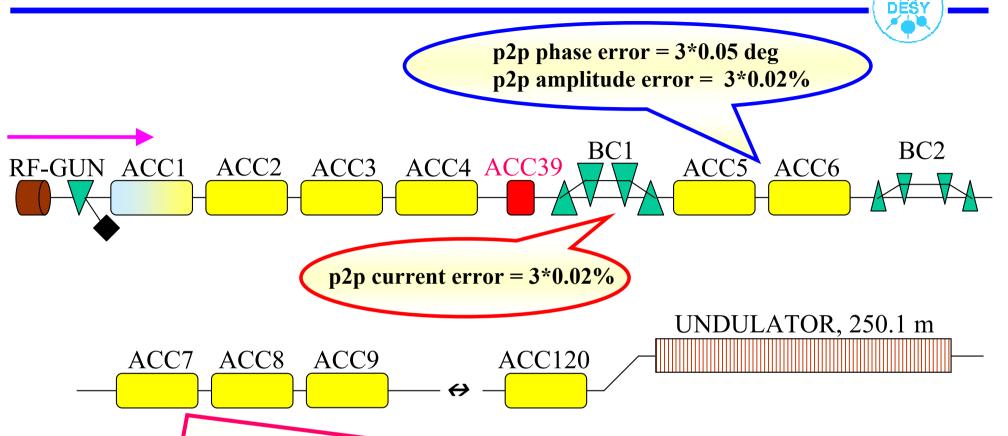

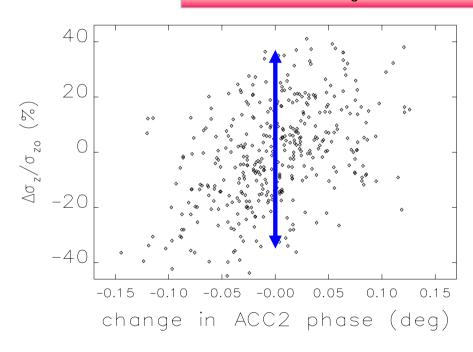

# **S2E Simulations Under Same Jitter Tolerances**

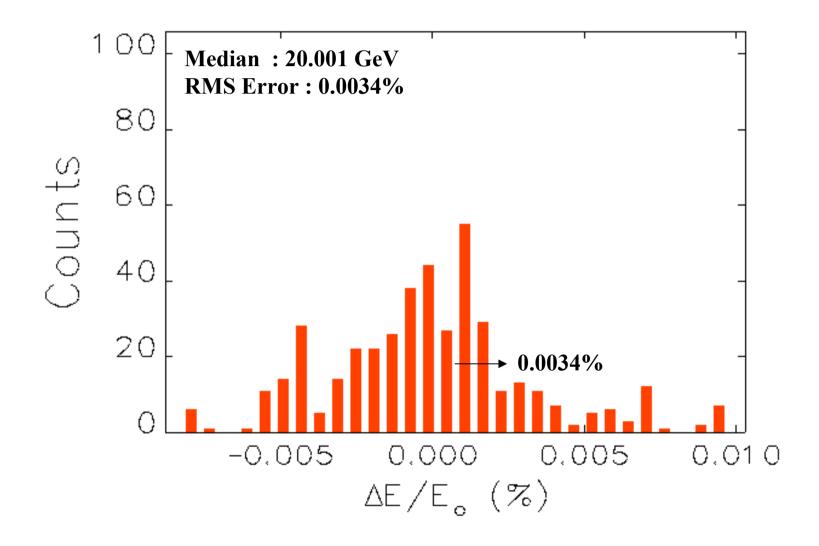

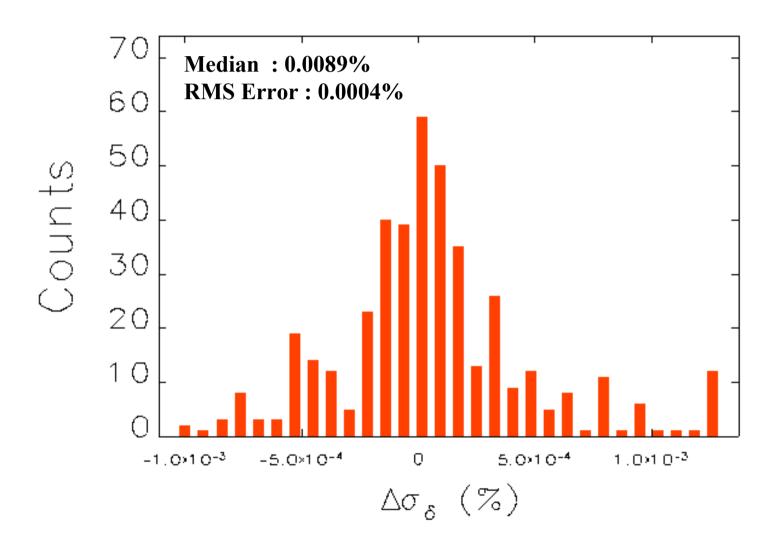

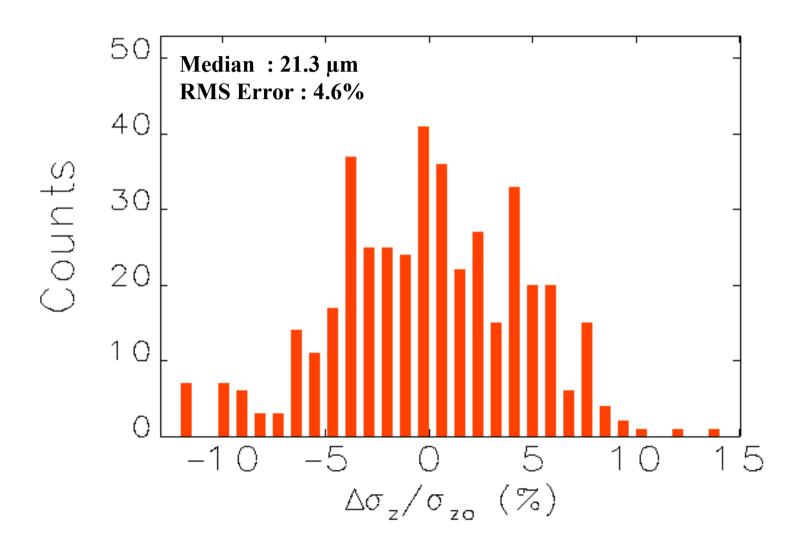

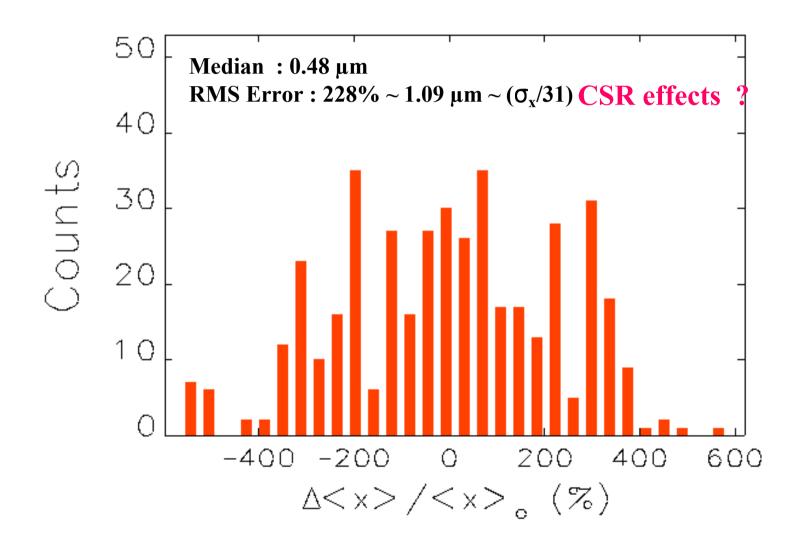

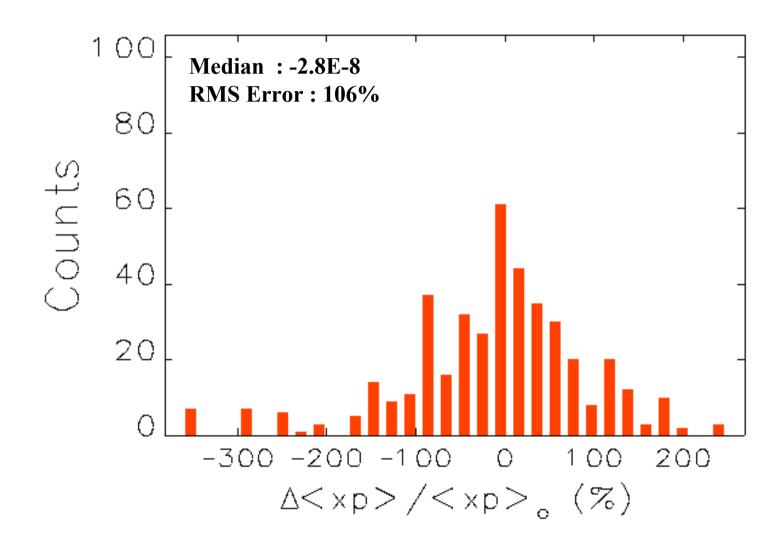

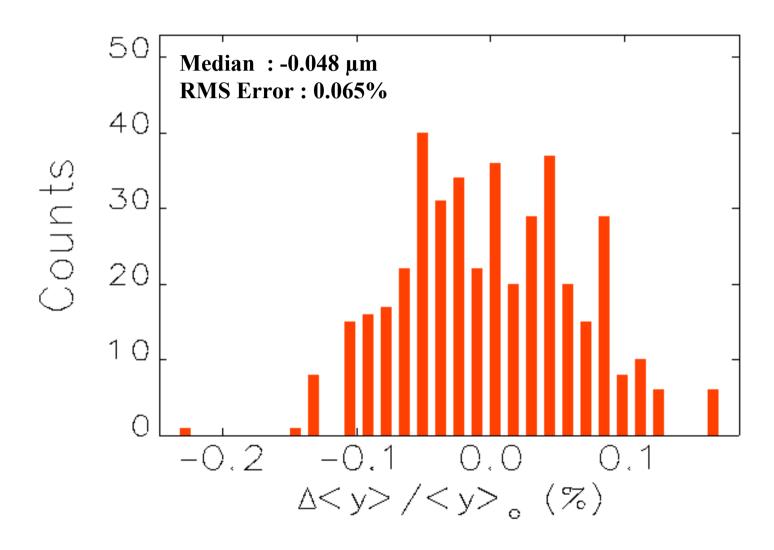

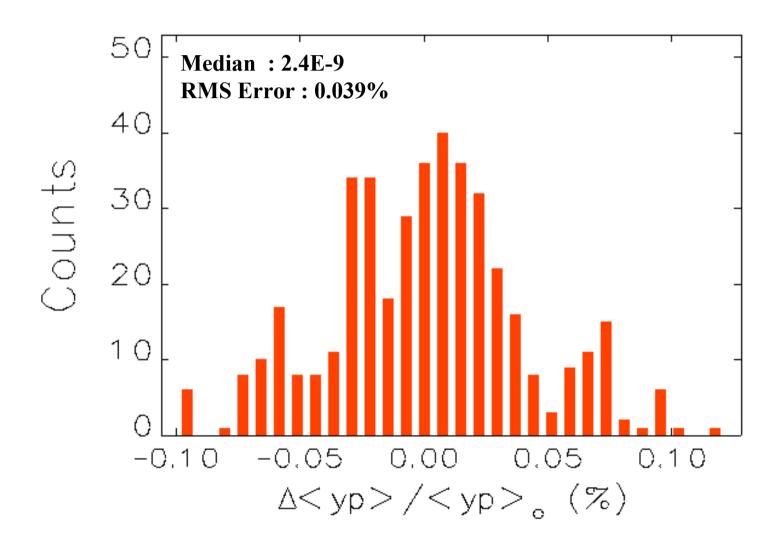

After applying random error set ( $p2p = 3 \times tolerance$ ) to each component, we have performed about 400 times S2E simulations from gun to the end of linac to compare two linac layouts under same jitter tolerance set (TOL-I).

**400 Times Tracking with Curent Layout**

**400 Times Tracking with Alternative Layout**

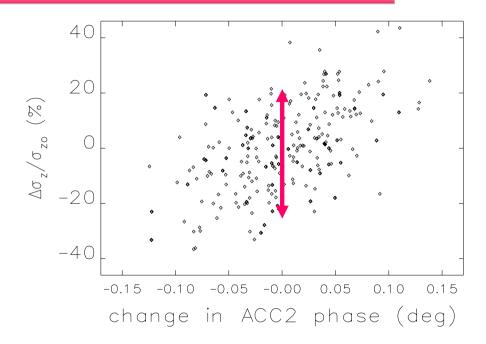

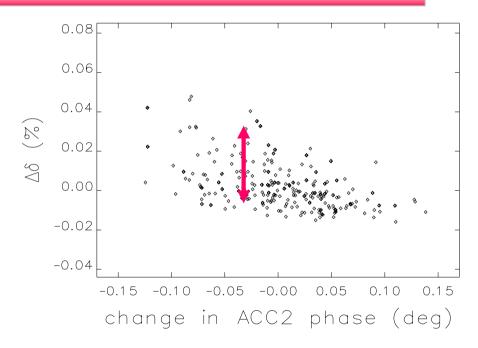

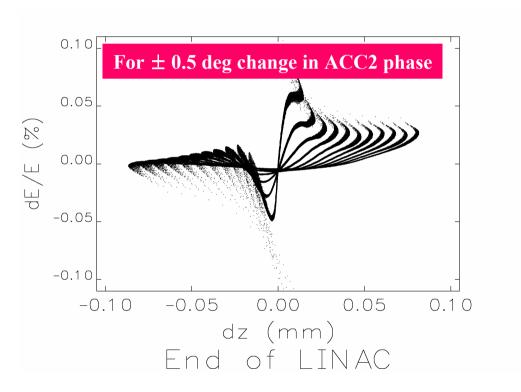

#### most sensitive jitter source on bunch length = ACC2 phase error

wider change in bunch length for current layout stronger correlation with errors in other components!

400 Times Tracking with Curent Layout 400 Times Tracking with Alternative Layout

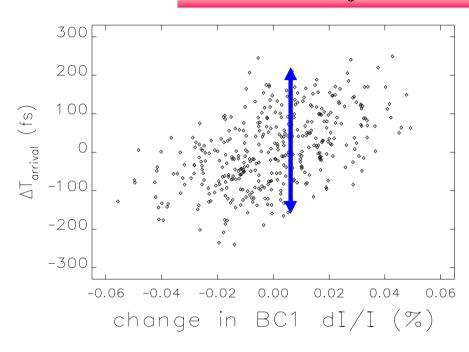

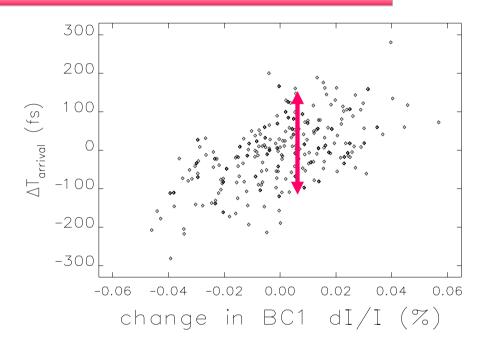

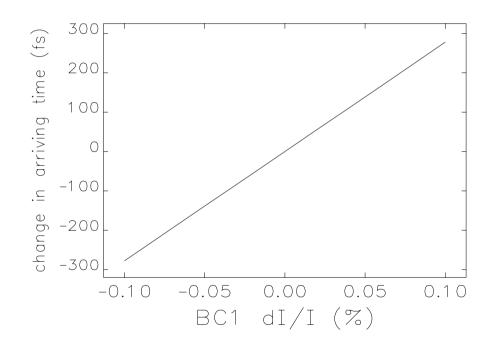

#### most sensitive jitter source on arriving time = BC1 current error

wider change in bunch arriving time for current layout stronger correlation with errors in other components!

**400 Times Tracking with Curent Layout**

400 Times Tracking with Alternative Layout

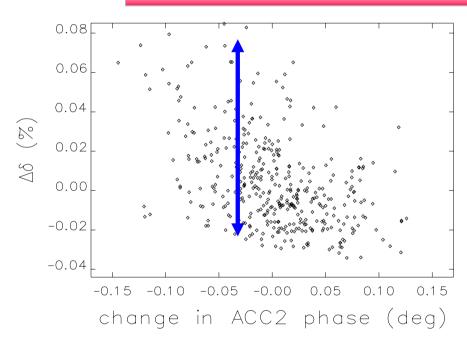

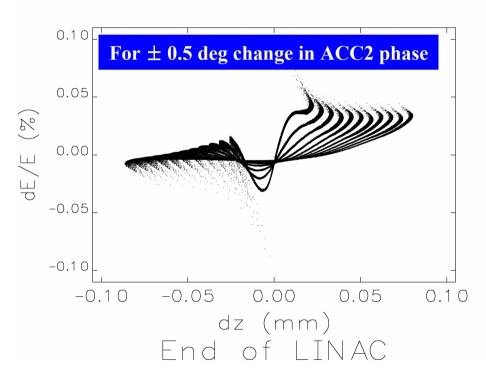

#### most sensitive jitter source on p2p energy deviation = ACC2 phase error

wider change in p2p energy deviation for current layout stronger correlation with errors in other components!

400 Times Tracking with Curent Layout 400 Times Tracking with Alternative Layout

#### most sensitive jitter source on average energy = DBC2 voltage error

similar change in average energy for both layouts DBC2 is exactly same for both linac layouts

**400 Times Tracking with Curent Layout**

**400 Times Tracking with Alternative Layout**

# **Newly Updated Controllable Jitter Tolerance**

#### **According to Dr. Simrock's LINAC2004 Talk:**

For both 1.3 GHz TESLA Module & 3.9 GHz 3<sup>rd</sup> Harmonic Module

For the short term period (1 min)

RF Phase Error < 0.02 degree (rms)

RF Amplitude Error (dV/V) < 0.02% (rms)

New Reference!

Controllable jitter tolerance depends on charge fluctuation!

$$Q = Q_0 (1 + 0.03 \Delta \phi_1) (1 + (\Delta E / E)_1) (1 + (\Delta V / V)_g)$$

Dr. Simrock confirmed that these can be reduced to 0.01 deg and 0.01% soon.

# **New Threshold of Jitter Sensitivity**

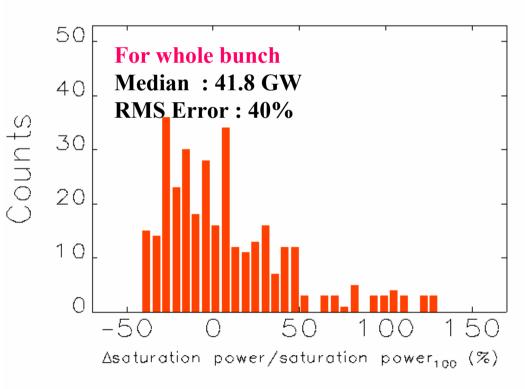

By the help of S2E simulations, let's apply artificial jitter or error to all important components (GUN, ACC1 ~ ACC120, ACC39, BC1 and BC2) in order to investigate the jitter sensitivity  $J_s$  of those components on the FEL performance at the undulator (SASE1).

After considering controllable jitter tolerances in the near future, we have determined new thresholds of jitter sensitivity, which are related with FEL performance (Applying Ming Xie Model to SASE1):

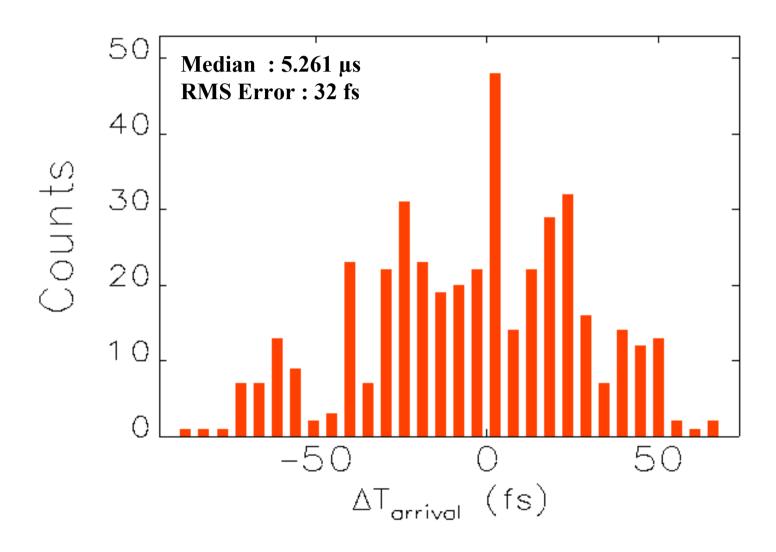

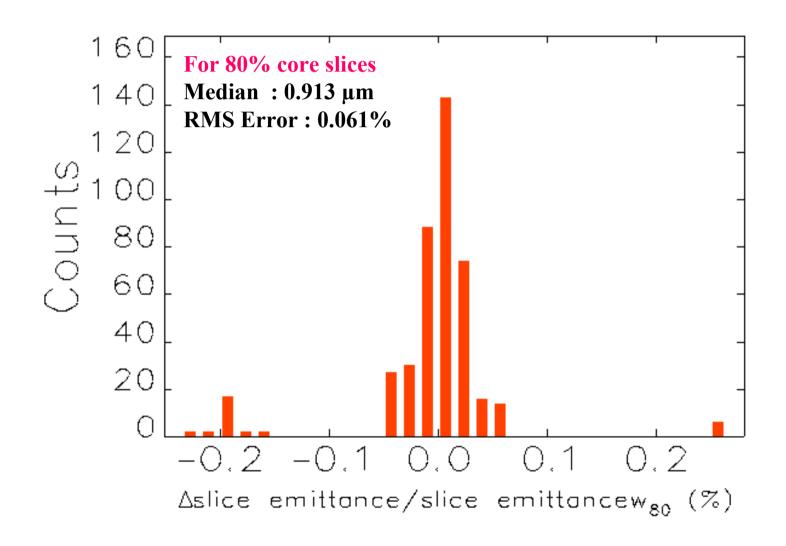

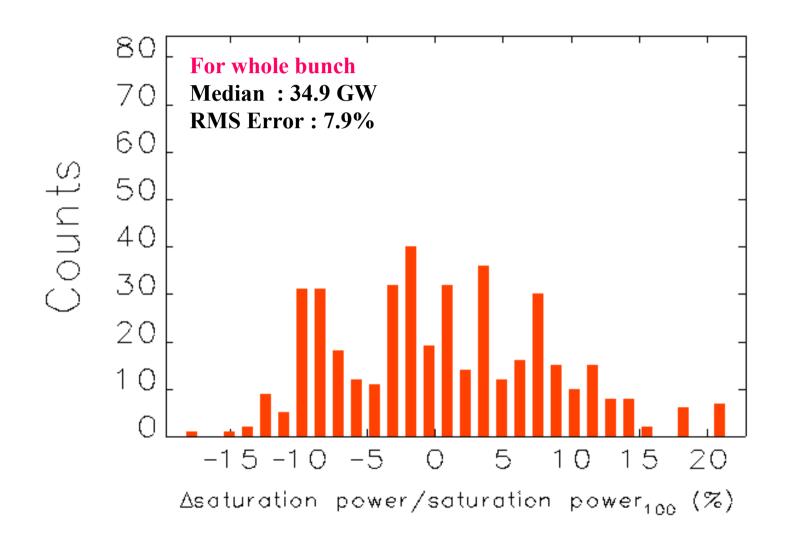

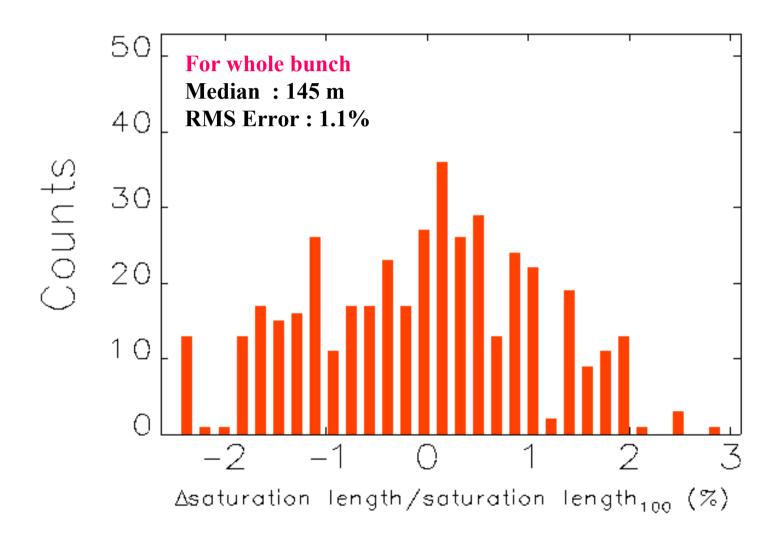

Peak-to-peak (p2p) change in SASE source wavelength should be within  $\pm 0.022\%$ Peak-to-peak (p2p) change in saturation length should be within  $\pm 1.6\%$ Peak-to-peak (p2p) change in saturation power should be within  $\pm 15\%$ Peak-to-peak (p2p) change in bunch arrival time should be within 36 fs (=0.5 $\sigma_{\tau}$ )

Then choose the jitter tolerance  $J_t$  which gives  $\sqrt{\sum_{i=1}^{n} \left(\frac{J_{t,i}}{J_i}\right)^2} < 1$

$$\sqrt{\sum_{i=1}^{n} \left(\frac{J_{t,i}}{J_{s,i}}\right)^2} < 1$$

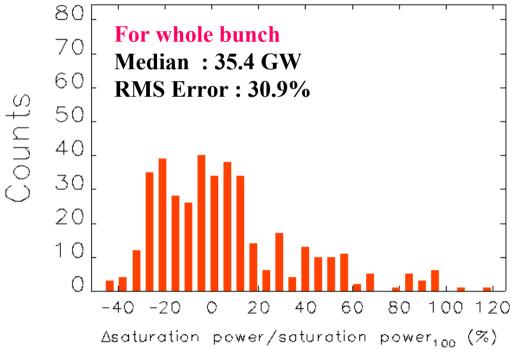

Then we have checked overall FEL performance under random tolerances set by repeating about 400 times S2E simulations.

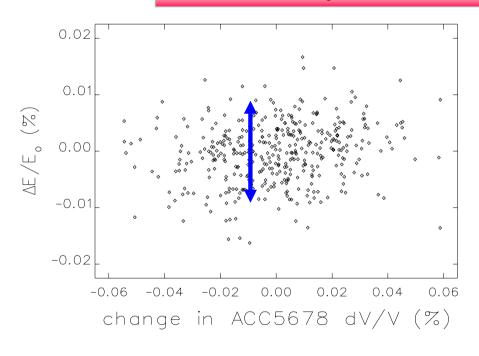

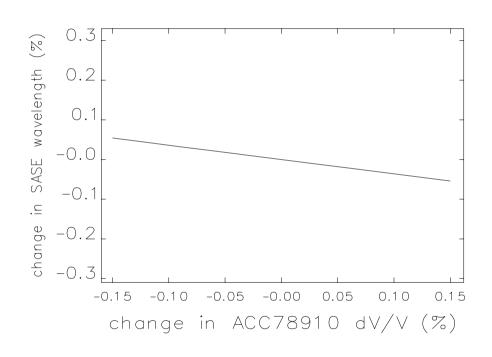

#### **Alternative Layout with 2BC**

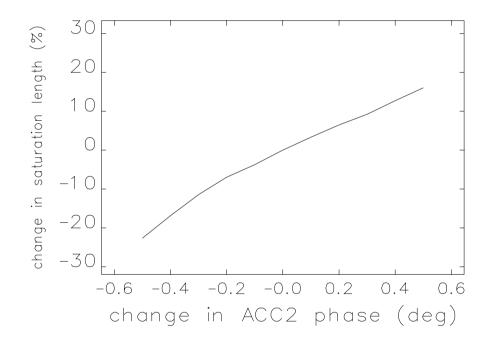

#### ACC78910 dV/V is the most sensitive jitter source to wavelength ACC234 Phase is the most sensitive jitter source to saturation length

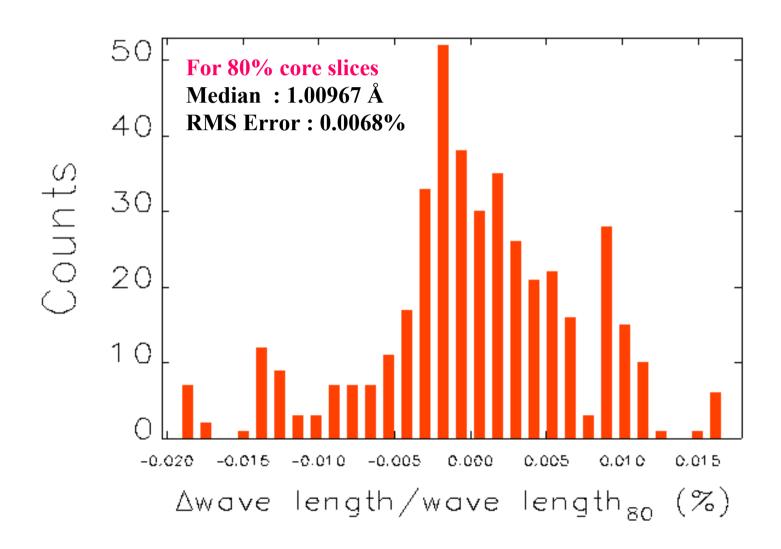

p2p sensitivity in wavelength  $\sim \pm 0.06\%$ p2p change in wavelength  $\sim \pm 0.022\%$

p2p sensitivity in sat. length  $\sim \pm 0.06$  deg p2p change in sat. length  $\sim \pm 1.6\%$

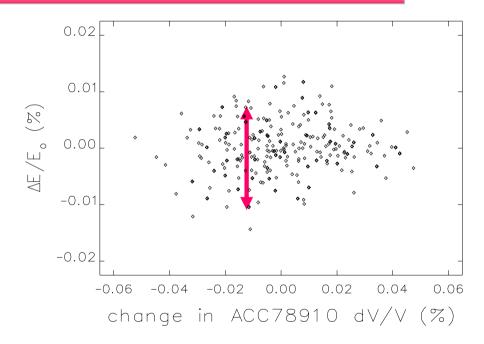

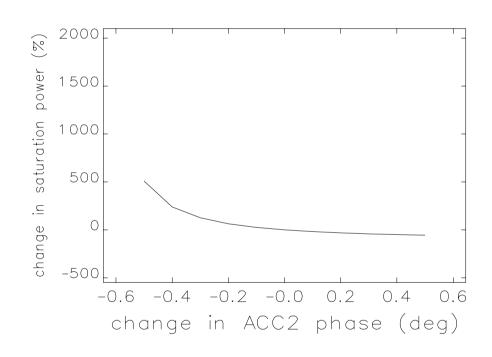

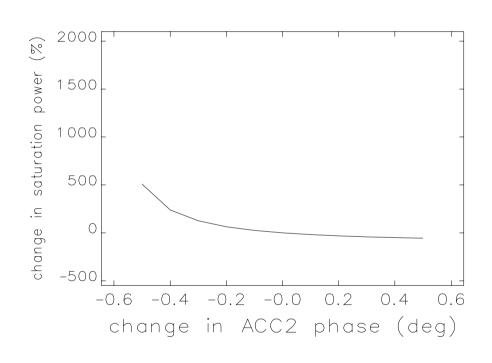

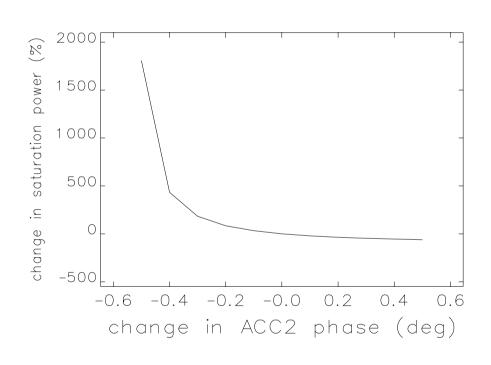

#### **Alternative Layout with 2BC**

#### ACC234 Phase is the most sensitive jitter source to saturation power BC1 dI/I is the most sensitive jitter source to arriving time

p2p sensitivity in sat. power  $\sim \pm 0.06\%$ p2p change in sat. power  $\sim \pm 15\%$

p2p sensitivity in arriving time  $\sim \pm 0.004\%$ p2p change in arriving time  $\sim \pm 36$  fs

#### **Alternative Layout with 2BC**

#### ACC234 Phase is the most sensitive jitter source to saturation power and saturation length

weak over-compression against ACC234 phase error

#### **Current Layout with Double Chicane**

# ACC234 Phase is the most sensitive jitter source to saturation power and saturation length

strong over-compression against ACC234 phase error

# Sensitivity & Tolerance for Alternative Layout

#### **FEL Performance Based Tolerance**

|                       | Sensitivity(p2p)  | <b>Tol.</b> ( <b>p2p</b> ) | Tol. (rms)       | Threshold              |

|-----------------------|-------------------|----------------------------|------------------|------------------------|

| dT                    | ± 0.729 ps        | ± 0.300 ps                 | 0.100 ps         | saturation length      |

| dQ/Q                  | $\pm 5.452\%$     | $\pm$ 3.000%               | 1.000%           | saturation length      |

| ACC1C1234 phase       | $\pm$ 0.133 deg   | $\pm$ 0.045 deg            | 0.015 deg        | saturation length      |

| <b>ACC1C1234 dV/V</b> | $\pm$ 0.129%      | $\pm$ 0.045%               | 0.015%           | arriving time          |

| ACC1C5678 phase       | $\pm$ 0.072 deg   | $\pm$ 0.045 deg            | 0.015 deg        | saturation power       |

| ACC1C5678 dV/V        | $\pm$ 0.063%      | $\pm$ 0.045%               | 0.015%           | arriving time          |

| ACC234 phase          | $\pm$ 0.048 deg   | $\pm$ 0.045 deg            | 0.015 deg        | arriving time          |

| ACC234 dV/V           | $\pm$ 0.045%      | $\pm$ 0.045%               | 0.015%           | arriving time          |

| ACC39 phase           | $\pm$ 0.064 deg   | $\pm$ 0.045 deg            | 0.015 deg        | saturation power       |

| ACC39 dV/V            | $\pm$ 0.142%      | $\pm$ 0.045%               | 0.015%           | arriving time          |

| BC1 dI/I              | $\pm$ 0.013%      | $\pm$ 0.012%               | 0.004%           | arriving time          |

| ACC56 phase           | $\pm$ 0.721 deg   | $\pm$ 0.045 deg            | <b>0.015 deg</b> | arriving time          |

| ACC56 dV/V            | $\pm$ 0.913%      | $\pm$ 0.045%               | 0.015%           | saturation length      |

| BC2 dI/I              | $\pm$ 0.201%      | $\pm$ 0.012%               | 0.004%           | arriving time          |

| ACC78910 phase        | $\pm 10.037 \deg$ | $\pm$ 0.045 deg            | 0.015 deg        | <b>SASE</b> wavelength |

| ACC78910 dV/V         | ± 0.060%          | ± 0.045%                   | 0.015%           | SASE wavelength        |

# **Summary**

After considering the space charge force at Gun, CSR in BCs, and geometric wakefields in linac, we have investigated jitter tolerance with an alternative European XFEL layout, and compared with that of current layout.

All jitter sensitivities becomes weaker when we use alternative linac layout.

Jitter correlation with other components is also reduced when we use alternative linac layout.

If we can control all phase (voltage) errors within 0.015% (0.015 deg), jitter effect in the alternative layout is weak enough to satisfy users' requirements.

# Acknowledgments

Y. Kim sincerely thanks S. Simrock, M. Borland, P. Emma, S. Schreiber, J. S. Oh, Dr. R. Brinkmann, Professor J. Rossbach, Professor I. S. Ko, Professor W. Namkung, Professor Kwang-Je Kim for their encouragements of this work and many useful comments and discussions on the jitter issues.